上升沿触发后,延时输出能否实现?

时间:10-02

整理:3721RD

点击:

请教各位:

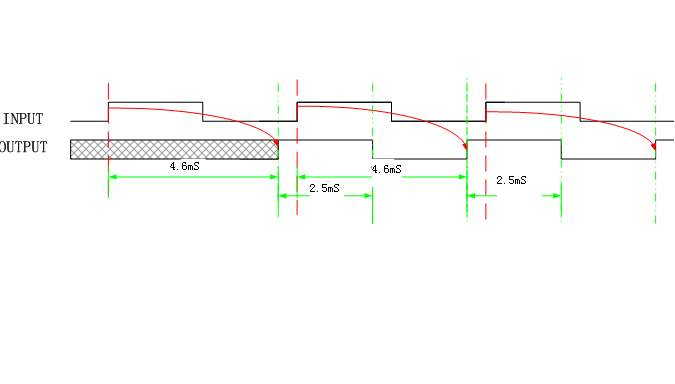

如图所示,能否用Verilog实现?

就是用INPUT的上升沿触发后,延时4.6mS后OUTPUT输出高电平,再经过2.5mS后OUTPUT输出低电平。

如图所示,能否用Verilog实现?

就是用INPUT的上升沿触发后,延时4.6mS后OUTPUT输出高电平,再经过2.5mS后OUTPUT输出低电平。

上升沿触发后,延时输出能否实现?

可以

需要一个时钟信号

上升沿触发后,延时输出能否实现?

用一个高的时钟进行延时计数,即可实现!

延时精度由计数时钟决定!

上升沿触发后,延时输出能否实现?

时钟频率是关键,既要能计出4.6ms又要保证input和时钟同步

上升沿触发后,延时输出能否实现?

谢谢各位指点。

各位高人是否再指点一下迷津。

我不知怎样才能做到用INPUT的上升沿来触发计数器工作?

上升沿触发后,延时输出能否实现?

把input用寄存器打两拍,前次为低,后次为高,既是上升沿。