FPGA基础学习笔记--时序逻辑电路-寄存器

时间:10-02

整理:3721RD

点击:

寄存器

寄存器是D触发器集合,不过其有位宽,将前述D触发器语句改为 input D;outpu Q;改为input [7:0]D;outpu[7:0] Q;即构成一个8b的异步复位寄存器。

寄存器文件

将寄存器以数组整合起来,并加上输入地址,输出地址,即构成可临时快速数据存储的寄存器文件。

示例代码

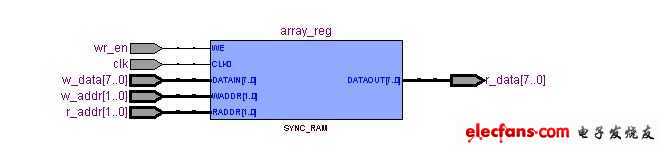

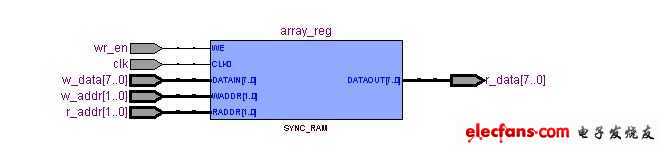

RTL级视图

FPGA EP2C8Q中每个LE含有一个异步复位、同步使能的D触发器,4个LUT。如果用寄存器存储数据将消耗很多LE,建议用

器件内嵌的RAM。

寄存器是D触发器集合,不过其有位宽,将前述D触发器语句改为 input D;outpu Q;改为input [7:0]D;outpu[7:0] Q;即构成一个8b的异步复位寄存器。

寄存器文件

将寄存器以数组整合起来,并加上输入地址,输出地址,即构成可临时快速数据存储的寄存器文件。

示例代码

- module reg_file

- #(

- parameter B=8,

- parameter W=2

- )

- (

- input clk,

- input wr_en,

- input [W-1:0] w_addr,

- input [W-1:0] r_addr,

- input [B-1:0] w_data,

- output [B-1:0] r_data

- );

-

- reg [B-1:0] array_reg[2**W-1:0];

-

- always @ (posedge clk)

- if(wr_en) array_reg[w_addr]<=w_data;

-

- assign r_data=array_reg[r_addr];

-

- endmodule

RTL级视图

FPGA EP2C8Q中每个LE含有一个异步复位、同步使能的D触发器,4个LUT。如果用寄存器存储数据将消耗很多LE,建议用

器件内嵌的RAM。

这个都是基础的啊

这个 不是我哦喜爱那个样的

额。

喜欢基础的。刚开始学好头疼==