基于FPGA的选通脉冲

时间:10-02

整理:3721RD

点击:

过程:

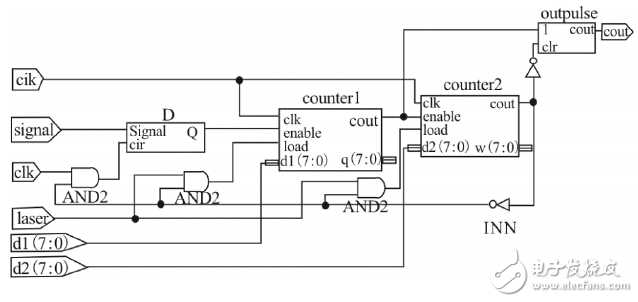

1)当有一个触发信号 signal 到达时,触发 D模块,产生使能信号 enable 使启动计数器 counter1,第一个计数器开始减计数,此时溢出端为低电平,而计数器 counter2 的使能端被计数 counter1 输出的低电平所封锁,不计数。

(2)当第一个计数器减到 0,计数器溢出,输出端变为高电平,使 outpulse 模块产生高电平信号(即选通信号),同时使计数器 2 使能端为“高”,启动计数器 2 开始减计数。

(3)当第二个计数器减到 0 时,计数器溢出,输出端变为高电平,使 outpulse 模块复位,完成一个选通脉冲的过程。同时通过一个反相器分别和 D触发器的清零端,第一个计数器,第二个计数器的置数端相,使 D 触发器清零,同时分别将选通门宽和延迟时间重新置入,等待下一次触发信号的到来,如此可以反复循环,不断的进行触发产生选通脉冲。

是的啊,这种程序对于大神们来说应该不难吧

有懂得吗。鄙人扣扣1127079194