3D DRAM发展路径

因此,为了要延长DRAM这种存储器的寿命,在短时间内必须要采用3D DRAM解决方案。什么是3D超级DRAM (Super-DRAM)?为何我们需要这种技术?

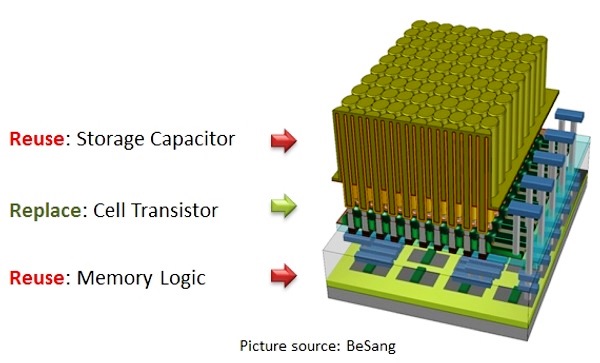

平面DRAM是存储器单元阵列与存储器逻辑电路分占两侧,3D Super-DRAM则是将存储器单元阵列堆叠在存储器逻辑电路的上方,因此裸晶尺寸会变得比较小,每片晶圆的裸晶产出量也会更多;这意味着3D Super-DRAM的成本可以低于平面DRAM。

3D Super-DRAM重复使用了运用于平面DRAM的经证实生产流程与元件架构;当我们比较平面与3D两种DRAM,储存电容以及存储器逻辑电路应该会是一样的,它们之间的唯一差别是单元电晶体。平面DRAM正常情况下会采用凹型电晶体(recessed transistor),3D Super-DRAM则是利用垂直的环绕闸极电晶体(Surrounding Gate Transistor,SGT)

平面DRAM最重要也最艰难的挑战,是储存电容的高深宽比。如下图所示,储存电容的深宽比会随着元件制程微缩而呈倍数增加;换句话说,平面DRAM的制程微缩会越来越困难。根据我们的了解,DRAM制程微缩速度已经趋缓,制造成本也飙升,主要就是因为储存电容的微缩问题;这个问题该如何解决?

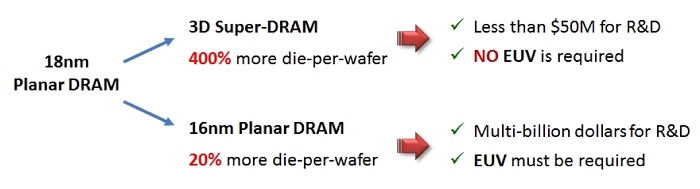

平面DRAM的储存电容恐怕无法变化或是修改,但是如果使用存储器单元3D堆叠技术,除了片晶圆的裸晶产出量可望增加四倍,也能因为可重复使用储存电容,而节省高达数十亿美元的新型储存电容研发成本与风险,并加快产品上市时程。

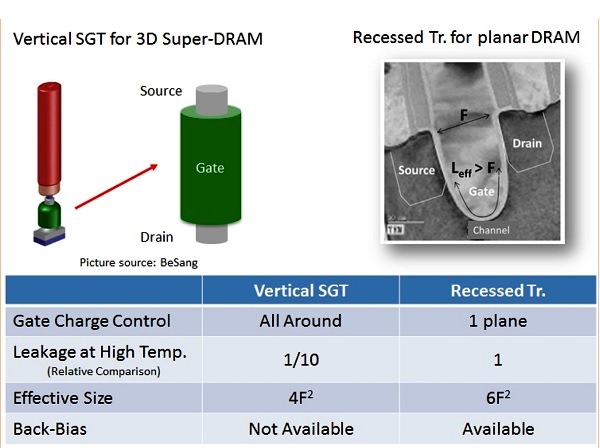

垂直SGT与凹型电晶体有什么不同?两者都有利于源极(source)与汲极(drain)间距离的微缩,因此将泄漏电流最小化;但垂直SGT能从各种方向控制闸极,因此与凹型电晶体相较,在次临限漏电流(subthreshold)特性的表现上更好。

众所周知,绝缘上覆矽(SOI)架构在高温下的接面漏电流只有十分之一;而垂直SGT的一个缺点,是没有逆向偏压(back-bias)特性可以利用。整体看来,垂直SGT与凹型电晶体都能有效将漏电流最小化。

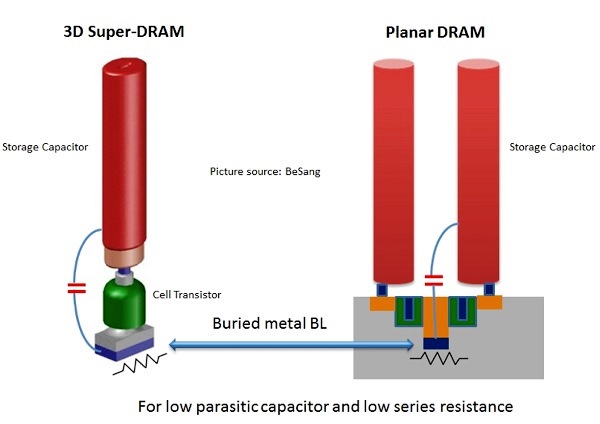

接着是位元线寄生效应(parasitics)的比较。平面DRAM的埋入式位元线能减少储存电容与位元线之间的寄生电容;垂直SGT在最小化寄生电容方面也非常有效,因为位元线是在垂直SGT的底部。而因为垂直SGT与埋入式电晶体的位元线都是采用金属线,位元线的串联电阻能被最小化;总而言之,垂直SGT与凹型电晶体的性能与特征是几乎相同的。

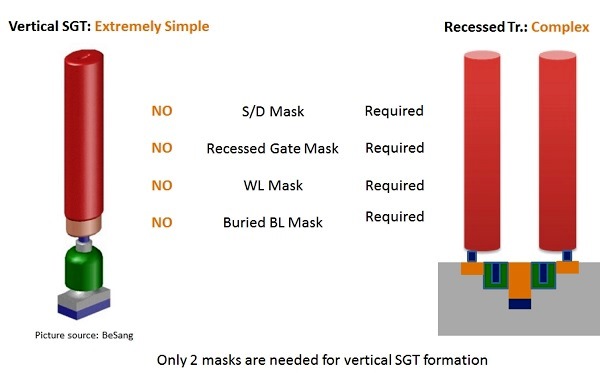

不过垂直SGT与凹型电晶体比起来简单得多,前者只需要两层光罩,节省了3~4层光罩步骤;举例来说,不用源极与汲极光照,也不需要凹型闸极光罩、字元线(word line)光罩,以及埋入式位元线光罩。如果你有3D Super-DRAM制造成本高昂的印象,这是不正确的;3D Super-DRAM的制程与结构,还有元件的功能性与可靠度都已成功验证。

垂直SGT需要的光罩层数较少

下图是3D Super-DRAM与平面DRAM相较的各种优点摘要:

早在07年工业界用的就是这样的access Tr

具体到为什么DRAM不把逻辑电路放在下面 我不太了解估计是因为对于走线没有帮助吧

不就是环栅晶体管多层三维集成吗,工艺成本得以降低,寄生效应得以减小,性能上没有

损失,容量上明显扩大。这不就是itrs2.0所说的三维功率集成吗。