Verilog仿真遇到诡异的事情

时间:12-12

整理:3721RD

点击:

仿真器是Modelsim 10.1C

仿真一个比较大的系统,下面有几十个module

某一个module中一句简单的verilog赋值语句:

assign PHY_TXD00_new[9:0] = PHY_TXD00_tmp[9:0];

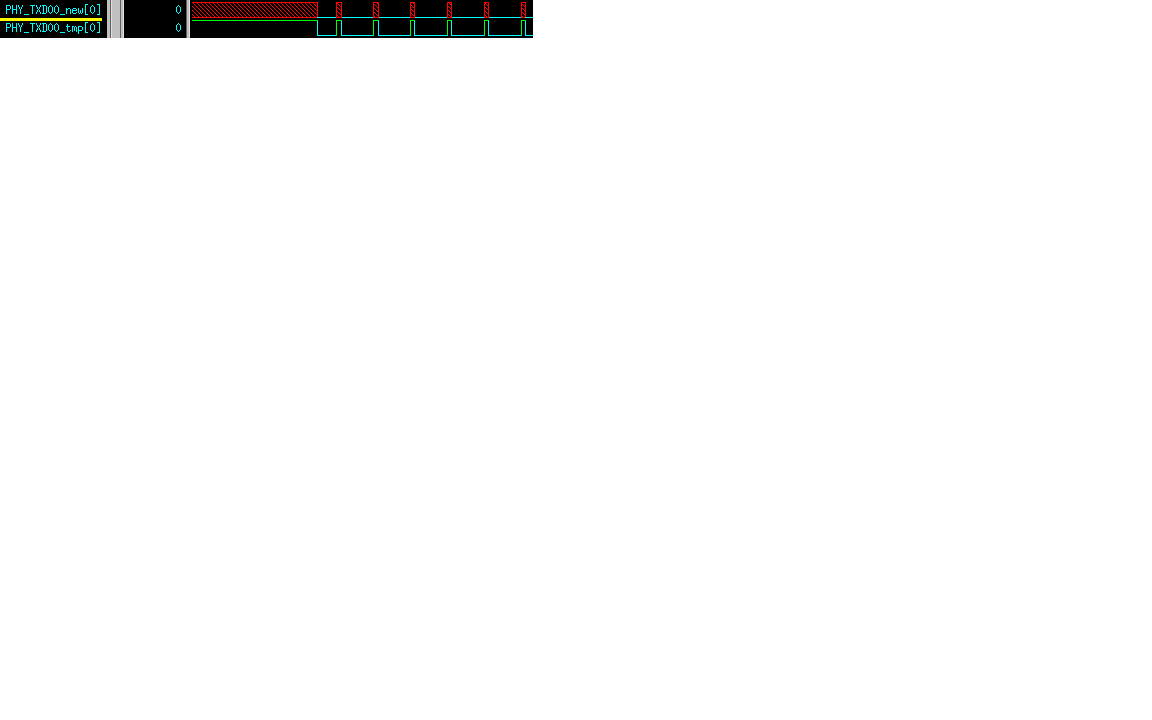

从波形中看PHY_TXD00_tmp正常,但是PHY_TXD00_new出现红色unknown,凡是应该高电平的地方都是X,这也太奇怪了,assign后就值不一致了

想了一天没想明白咋回事,贴到版上求大侠指点指点!

谢谢!

仿真一个比较大的系统,下面有几十个module

某一个module中一句简单的verilog赋值语句:

assign PHY_TXD00_new[9:0] = PHY_TXD00_tmp[9:0];

从波形中看PHY_TXD00_tmp正常,但是PHY_TXD00_new出现红色unknown,凡是应该高电平的地方都是X,这也太奇怪了,assign后就值不一致了

想了一天没想明白咋回事,贴到版上求大侠指点指点!

谢谢!

波形

代码有多重赋值了吧

您是说Multi-driven吗,确实没有啊,我这信号名起的都是独一无二的

改成always写法试试呢

always@( * ) begin

a = b;

$display("debug");

end

这个波形就是了冲突了的典型波形

好的,我试试

您说的冲突了是指?能说的详细点么,谢谢

就是有多个驱动

如果没有多重赋值,看看是不是端口上冲突了。

有没有可能时外部直接赋值了?

没有verdi或debussy吗

trace一下这个信号有几个driver不就行了

感觉信号被拉住,应该可以trace到,看接口什么的有没有force住。

另外定一下技术贴,哈,版上技术贴不多,支持一下。

多重赋值的话modelsim不会报错么。

不会

multi drive啊。。。。多平常的事儿。。。。。=,=

赋值冲突,不同地方赋值了。

虽然转行不做芯片了,看到波形还是很亲切啊。

multi drive,可能case里面也force或者看看信号定义,有无驱动强度相关引入。

转行做啥了?

找到问题了吗,是不是多重赋值呢,解决了的话说明一下原因呢,看看大家猜的对不对

除了大家说的multi drive

还有个可能,你看的文件,和你仿真用的文件,不是同一个版本