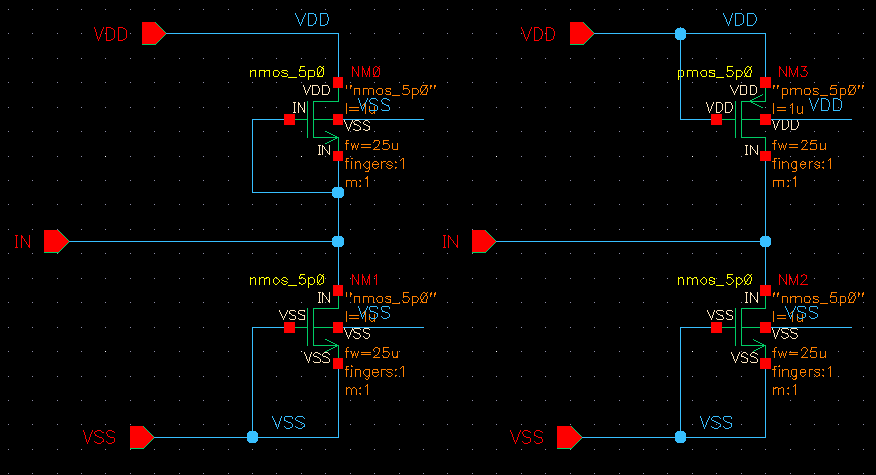

求比较两种简单ESD电路优缺点

一般文献是用的右边这种,但我们现在是用的左边的。

不知到左边比右边的好在哪里,有人能分析下吗。

我觉得可能是没有latch up,因为只有N管?

可以用在辐射环境下?

谢谢!(图好像要点一下才显示全)

老兄估计只是弄了个示意图,右边的确是通常用的ESD,但是由于NPN与PNP的特性不同,P管和N管的尺寸相差却是很大的,而不是一样(图片中管子尺寸相同)。

左边的电路下边的N管是G-G结构,在输入相对于VSS有浪涌的时候,可以实现G-G的放电行为。

上边的N管在输入对于VDD的PIN的有浪涌的时候才能工作,工作的时候只是一个NPN的行为所产生的snapback曲线,而不是G-G行为。MOS管寄生的三极管和普通的三极管的特性有很大不同,慎用!

左边你们设计的电路的确不会产生栓锁效应。好处之一?

为什么左边的比右边的好?谁设计的找谁吧,我帮你灌灌水,顶顶贴

谢谢!右边只是从左边改的,尺寸不对。

还有左边的连GATE(容易击穿),也好像不太好,

不过有人说左边的好 :“左边的是比较合理的,利用NMOS的snapback特性,要注意几个转折点的电压。

右边的使用PMOS通常是不好的,PMOS击穿后其钳位电压是上升的,保护很弱的。”

若ESD版图正确,右边也不会出现latch-up

两边MOS尺寸都不对吧? 25um?多少伏ESD?

一般PMOS snapback不好做出来,所以上面也会用NMOS,或者直接开漏输出。上面的nmos负 pulse peak时,发生snapback。另外,只看这个图,没多少信息,重要的是看整体ESD方案如何,esd discharge bus是啥?只有地线?还是有电源线?要从电流路径来判断。

其他考虑,信息不全,不好判断,多少伏的MOS?breakdown多少?输入范围多少?电源多少?

谢谢。只看见别人版图是这么做的,2.5V电压,电源和地没有其它措施了。

您的意思是说左边那个其实要好点,要实用点吗?

不过有个主要的问题:其输入接gate了,这个在比较快的ESD来时,

应该很容易被打坏(衬底为0电位),

造成短路。从这点来看,是否没有用PMOS好呢?

左边不会闩锁的结论是如何得到的?电源总会接pmos的,就看距离远近了,无论如何NMOS的漏接电源都是要尽量避免的行为吧?

不客气,只是我的理解而已,

Mos 管 break down电压多少呀,snapback 之前没有break down就行,MOST是什么类型的?是否厚栅?

我觉得先从版图上确定电流路径(管子大,线粗的地方),在判断功能比较容易一些,呵呵