vcs的一个诡异的仿真错误

always_ff @(posedge SCL4IP)

begin:EEDinBuf_block

if (!OSC_EN) begin //not programing IP.

if (STP_SR && STP_S && !READ) begin

EEDinBuf[BITSEL] <= EEDBI;

end

end

end

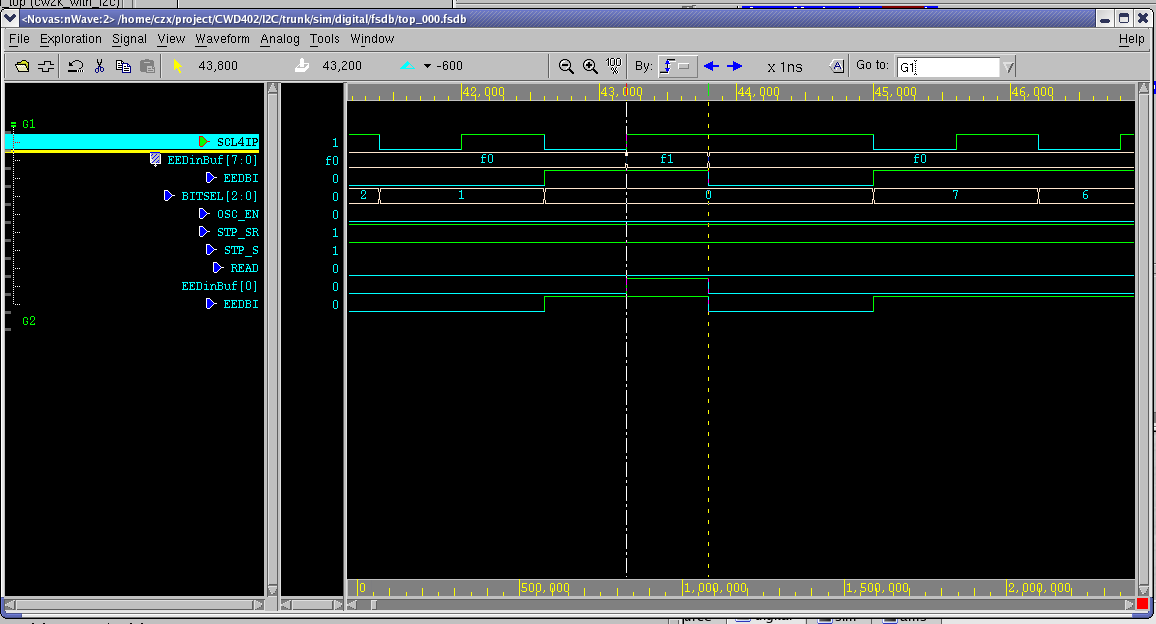

其中 osc_en,stp_sr,stp_s, read这几个信号一直保持不变,在白色光标线出, SCL4I

P的上升沿,EEDinBuf改变正常,但是诡异的是,

在黄色光标处,EEDinBuf的最低位居然跟着EEDBI发生改变了,这个时候SCL4IP 一直=1

,按理不能变啊。

请大家讨论讨论,看看这个是个什么可能。

试过assign SCL4IP_DB = #50 SCL4IP, 然后always @(posedge SCL4IP_DB) .... 就没

有问题了。

看波形这上面也没有什么glitch 啊。 vcs有什么控制glitch的相关选项么?

谢谢大家

能否具体说说?

我不觉得理解有什么问题啊。

只有posedge时候才能发生变化,现在仿真scl4ip这个时钟保持不变,但是,data 却 改

变了,这个有问题吧。

而且这里也不存在setup、hold的问题

所有EEDinBuf 赋值的地方只有这一段

另外,如果是assign #0 SCL4IP_DB =SCL4IP;然后always @(posedge SCL4IP_DB)就会有

问题

assign #0.5 SCL4IP_DB = SCL4IP, 然后always @(posedge SCL4IP_DB) .... 就没有

问题

能怀疑的就是SCL4IP有glitch了。但是从波形上看,SCL4IP很光滑。分析它产生的条件

,貌似也不会有glitch。

所以想请教下是不是vcs 有什么选项可以控制glitch的显示之类的东西。

bitsel就是一个输入了。用来把EEDBI赋值给EEDinBuf的哪一位。

这个其实是很诡异的问题了。

我有单独写过一个测试code,脱离了这段code具体的环境,直接在testbench里面手工产

生SCL4IP,BITSEL等等, 理所当然的,仿真结果没有问题。。

所以还是怀疑vcs 认为SCL4IP有个glitch,但是波形上看不到,结果就产生了这个诡异

的结果。

verdi有个环境变量控制glitch的产生与否,好像带有GLITCH什么的,你搜一下verdi的文档就有了。

你这个很容易debug

@(signal)

$display(time and signal value)

就可以在log里看出来glitch了

谢谢。应该和verdi无关,用dve直接看也是这个结果

你没有理解。vcs自己肯定是有glitch信息的,关键是调用PLI的时候要不要这个信息写入FSDB,所以你应该查verdi的文档。

哦。 vcs 直接跑仿真调用 dve,也看不到glitch,那有可能两边都需要找glitch相关控

制选项吧。

刚刚试了一下,在43800.0000ns处, SCL4IP 先 =0, 然后还是43800.0000ns SCL4IP

= 1.

多谢指教。

那就对了,你那个带时间的assign会把glitch略掉,你可以看看惯性延迟的定义

en.之前的思路就是怀疑有glitch,然后用延迟来过滤掉。

novas的变量时NOVAS_FSDB_ENV_MAX_GLITCH_NUM,设置=0后

会dump所有的glitch,不过不知道是不是因为这个glitch是同

一时刻上发生变化,fsdb上面是看不到任何提示或者glitch波形

了。

vcs的manual看看搜索了一下,只有vpd格式里面有类似的glitch

控制选项。

gui里有个选项要打开的,你试试快捷键g啥的。要不就翻一下菜单,叫显示glitch什么的

重新验证了下,应该是一开始某个地方搞错了

现在 在makefile里面设置可以dump glitch了

谢谢各位的指教