关于allegro的铺铜与布线顺序的疑问

关于allegro的铺铜与布线的顺序疑问

目前我布线的一块板子遇到几个问题,就是关于allegro软件的布线和铺铜的先后顺序,以及操作手法。

主要问题描述如下:

1、应该是先布线还是先铺铜?我看到市面上关于allegro的书(《allegro 15.X 学习与使用》、《Cadence高速板设计与仿真》第二版)在内容安排上都是先讲了铺铜,然后才是布线。如果这样,我发现自动布线基本不可能再布通了,并且自动布线速度极慢。也听我一个同事说,应该先不布线再铺铜。不知道其中到底哪个顺序是正确的?!

2、铺铜的时候应该使用动态的还是静态的方式?还是如果先铺铜再布线就应该是使用动态的,而如果是先布线在铺铜就应该是静态的?我个人认为一直用到现在,明显动态有很大的优势,自动避让这个效果非常有用,不知道现在allegro还保留着静态铺铜有什么必要呢?

3、在gloss里面我加泪滴时候,如果先布线,在加泪滴,在铺铜,没有问题。但是如果先布线,再铺铜,再加泪滴,就会产生很多的shapes错误,不知道其中的顺序是什么,你遇到过这样的疑惑吗?还有就是自动平滑布线在什么进行,肯定是布线以后,但是在加泪滴后还是前?在铺铜后还是前?其实这个问题和第一个问题应该是一类的,就是布线中的顺序问题,我始终没找到比较好的正确的方法。希望你帮助以下

4、给你看一下布线后在铺铜的疑惑问题,就是如果我铺铜的NET设置为GND那么先前布线中有许多GND的PIN或者VIA都已经使用导线连接在一起了,我铺铜后肯定是希望他们不需要在使用导线了(极端的,一些孤铜的地方,普通不可到达的地方,还是需要导线拉出接入附近的GND铺铜上),或者就是从PIN拉出一小段线后打一个过孔就可以马上接地。但是如果先布了线,我怎么才能让后面铺铜的时候,ALLEGRO可以自己知道满足以上需要呢?

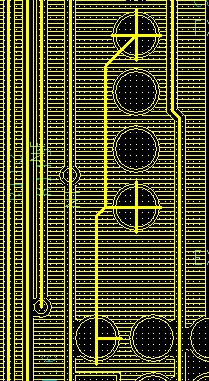

下面的图片就是我布线后铺铜出来的怪样子,铜箔上面还有走线,三个热焊盘已经自己接地了。

.jpg)

5、以前我记得画板子完成最后会在板子的比较大块的铜箔的地方打许多的VIA用来打通TOP和BOTTOM或者多层板各层的地(用来减少压差的)。我就是在板子的上面选择布线,然后在某块铜箔的地方,双击以下,这样我原先设置的VIA就会打上去(以前用的15.2)。但是目前我也这么打,一旦双击好板子,ALLEGRO就会自己切换板层,并且ETCH的线也一直跟着鼠标,不像以前那样简单的双击就是一个洞。你遇到过这样的问题吗?

首先你的问题文字太多是很详细,不过看起来累。

1、一般是先走线,后铺铜(当然有些电源的铜可能会先铺)为什么书上先讲铜,后讲布线,可能出于之前14.X与15.X版本一个很大的差别就是铺铜,因为14.X没有动态铜概念。

2、铺铜用静态还是动态要灵活运用。至于allegro为什么要保保留着静态铺铜,这是必需的。因为有些重要的电源或地,我们并不希望它会因为其它的铜或走线或pin脚而去避开。再有用静态的铜,我们也不用考虑两个铺叠一起时,到底是保留哪个铜为准,而让另一个铜避开。还有一个用静态的铜可以使你的电脑运行很快。而大量的动态铜,会让你的电脑运行很慢。

3、同第一点(个人不建议去做泪滴,现在的工艺很强了)

4、没有很好办法。一般的做法是不管走线在shape上的。因为这一点也不影响gerber效果,更不会影响生产。如果非要地的铜一铺上,走线就自动删除。那只有手工来做。不过我建议留着,因为我们在做下一次板子修改时,可能会删除地的shape,这时你会多出很多地未接的rats]

5、你注意一下,看一下,etch会跟着鼠标是,拉出的信号是不是已经不是gnd了。是其它信号或空信号了。

非常非常感谢。您的解答让我明朗许多。语言表达能力还是我很大的弱项。

您说的前面三点我基本得到解答,关于静态和动态铺铜,我还需要实践中好好练习一下

关于第四点,我知道导线在SHAPE上面出gerber不会有问题,但是那些VIA呢?很多都是完全多余的VIA了,并且不仅影响美观,同样会导致很多其他信号走线的困难。不知道,除了不管它以外,还有没有更好的方法,或许不那么智能,点一个命令就出来,但是起码可以解决VIA的那些问题。

第五点您说得对,我注意到了,已经解决

我也没有看到你的图,至于你说的第四点我也不清楚你的意思。本来你在没铺铜之前就近打via接地是很好的呀。

难道说你并不是多层板,而是双面板?但就算是双面板就近打过孔也是很好的呀。为什么会觉得它多出来了呢。除非是你双面板(top走线,bot铺地),一面铺地,另一面是走线来用,而这边你地铺不进来,而是很多pin都是通过一个top层的铜铺出来在某一个地方打过。而导制之前每个管脚的边的via多出来了。(不知道是不是这个意思),如果是这样,的确是没什么好办法。就只能删除的时候什么也不选只选via,然后框选你要删除的via。指望铺铜而让via自动移除。allegro还没有这个功能。

终于会上传图片了。大家看得到吗?

就是双面板

1