生成Netlist时产生的错误

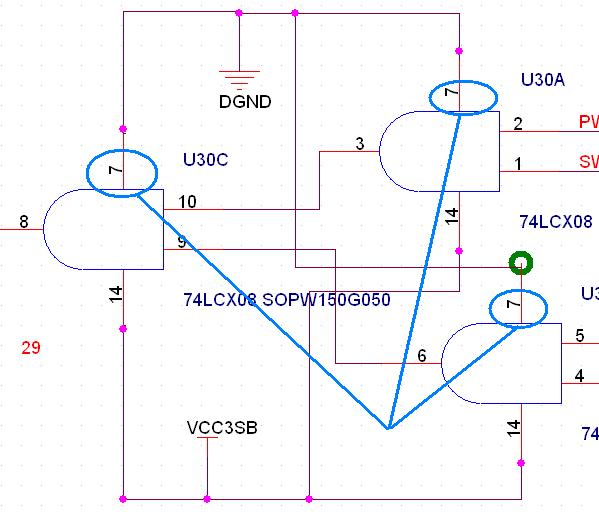

[FMT0003] Duplicate pin U30 pin 7. Possibly a complex hierarchy in logical view or duplicate part reference in physical view.

使用Orcad10.3不会有这样的提示

因为必须用9.2生成Netlist,但是提示这样的错误,不知道该怎么改?

怎么没人回呢?

需要把你的原理图的库修改掉。PIN7和PIN14是接电源和地的。这个元件被分成4个Part。每个部分都有 7和14 管脚,就重复了。生成Allegro的Netlist,是不允许这样的情况的。所以你只要在PartA里留下Pin7和Pin14,其他几部分就不要这两个管脚了。

有点烦,习惯了就好。

唉

谢谢小编了

虽然烦了点,但是还是要改,呵呵

还有个错误,希望大家帮忙解决,谢谢了

********************************************************************************

*

* Create Netlist

*

********************************************************************************

Netlist Format: allegro.dll

Design Name: F:\TEMP\LX800_PCB设计051226\ORCAD9.2TEST\LX800_060227.DSN

[FMT0018] Errors processing intermediate file

网上是这样说的:This generally means you have used an invalid character or formatting in a pin or part ref assignment. Most likely a space mistakenly added after a ref des ie. "U1 ". Ron O

但是那么多的Pin and Part REF,怎么才能迅速地找到错误的地方呢?