使用简易、策略选择精确度高的一款时序优化软件

报告人:林俊杰

论坛用户名:Hero2ljj

一、评估开展说明开展意义

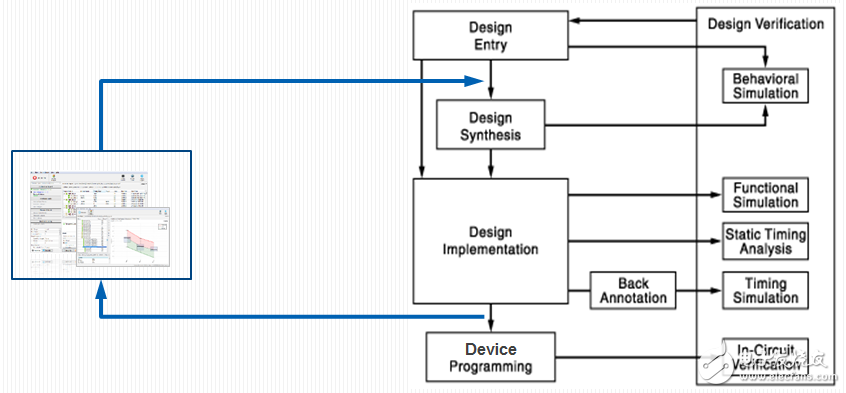

FPGA开发流程包括设计输入、功能仿真、综合优化、布局布线,其中综合优化和布局布线过程中需要考虑到时序约束实现问题。通常情况下如果时序约束无法满足要求,则需要重新查看代码设计,往复的进行前阶段流程,直到时序约束满足要求。在项目系统时钟较高,时序要求严格的情况下,该过程消耗大量的项目开发周期,降低该阶段周期可有效提高开发效率。

评估目标

InTime依据人工智能进行数据分析,能自动实现综合编译策略的选择。通过多次迭代,最终确定能满足时序约束的综合策略。通过本次的试用,验证InTime的可用性及有效性,为后续FPGA项目开发流程改进上提供可用的、高效的方案。

内容细分

1.软件环境

1)项目:

1.软件操作性

2.软件运行速率

2)方法:

1.安装开发软件,学习开发软件使用,评估软件易用性。

2.搭建工程,试探软件运行效率。

3.评估软件功能性。

3)意义:

1.良好的开发环境包括环境界面、报告分析等,保证软件具有较好可控性。

5)输出物:

1.软件功能概述

2.示例工程及说明

2.工程试验

1)项目:

1.验证Intime自动优化功能

2.验证Intime自动优化速率

3)方法:

1.利用FPGA实际工程项目为试验对象。

2.查看对比时序自动优化前后的结果。

3.统计自动时序优化消耗时间

4)意义:

1.以实际FPGA工程为对象进行实验,能有效的说明Intime的功能实用性。

2.通过前后时序优化结果及优化周期统计,验证软件在实际项目开发过程中,满足项目周期要求。

5)输出物:

1.示例工程

二、PLUNIFY简介

Plunify是一家电子设计自动化 (EDA) 软件公司,总部位于新加坡。Plunify的目标是要以云计算,机器学习以及数据分析技术来解决半导体晶片设计过程中所面对的问题。

在2011年,Plunify开发的云计算应用平台正式上线,是世界第一个专为半导体晶片设计的云平台。用户能透过这个平台,以随选式快速地得到服务器资源和软件工具。

Plunify在2013年正式发布旗舰产品 – InTime。InTime是一款针对FPGA综合与布局布线问题的专家软件。它利用大量且低价的云计算资源,通过机器学习和数据分析技术,在不需人工修改代码的情况下自动地达到更优越的设计结果。

InTime是一款使用大规模计算能力和机器学习来解决FPGA时序优化问题的软件。InTime 内嵌学习引擎,可以智能分析FPGA设计,为综合和布局布线提供更优的策略组合。同时,根据对器件、设计和工具特点的了解,以及独有的算法,InTime 可以生成最能满足设计需求的编译设置和设计约束。InTime 分析每一次编译结果,不断学习、丰富和更新自己的数据库。通过对计算资源的智能掌控,InTime 极大地帮助了FPGA工程师解决设计问题,并且使芯片性能显著提升。

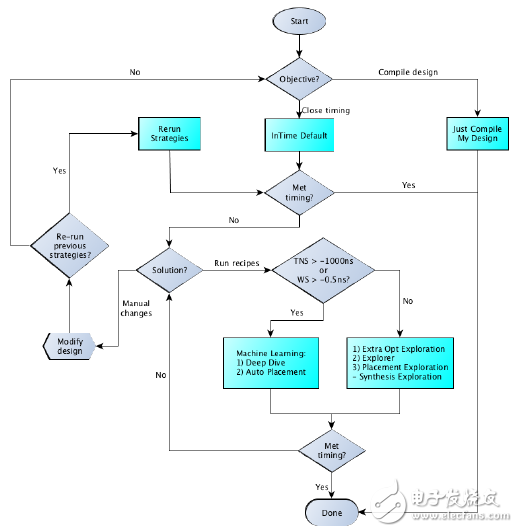

InTime实质上是一款综合器策略选择软件,支持Vivado和Quartus。实现Vivado、Quartus软件自动调用,自动填写综合策略指令。内嵌机器学习引擎,依据每一轮的编译综合结果,自动选择下轮运行策略。InTime运行流程如下图所示。

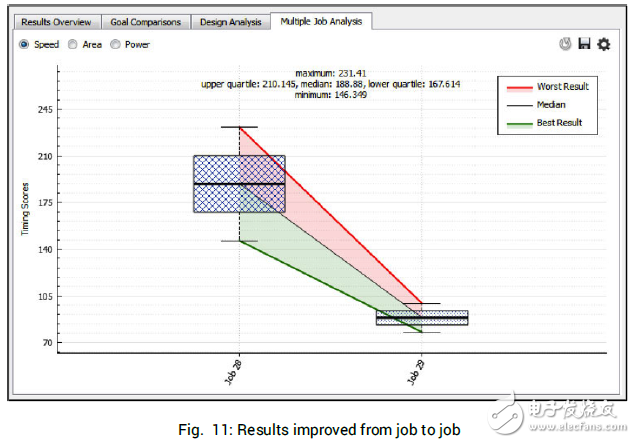

InTime自动在本地生成专属数据库,存储相关的设计信息。初始化运行时,依据综合器的选取,自动生成策略填入综合器优化选项。InTime支持多线程、多处理器分布计算,可为每个处理器分配特定的生成策略进行并行综合编译。编译结束后,利用机器学习引擎对编译结果进行分析学习,补充完善专属数据库设计信息,为下轮迭代运行提供策略生成依据。机器学习引擎主要关注时序、资源占用率、能耗。最终的优化结果呈现收敛趋势。

传统FPGA开发经过设计输入、设计综合、布局布线阶段,并依据综合编译结果选择是否再次进行时序优化。人工修改设计代码,多次运行编译后达到设计要求。InTime主要作用插入在设计综合和布局布线阶段,比对设计目标与当前运行结果,进行多次的自动迭代,降低人为参与,如下图所示。

“配方”是指 InTime 执行优化的关键设置选项。目前总共有四种类别的配方: Learning, Last-Mile, General以及 Advanced。Learning和Last-Mile,是用户进行分阶段优化时可采用的配方。当用户使用 InTime对某设计首次进行优化时,Plunify推荐使用Learning 类别。这个类别的配方会对设计的设置和约束进行初步分析和校准。例如 InTime default 配方会根据对以往结果的学习,调整所有可用的编译设置参数。当结果被 Learning 类别的配方充分提升后,执行Last-Mile类别的配方会进行更加具体的优化。例如,Placement Seed Exploration 配方仅仅改变编译设置的布局种子(placement seed)。最后, General 和 Advanced 类别下的配方更则多是出于可用性目的。

InTime运行流畅如下图所示,主要运行流程如下:

1.历史综合结果分析,提取运行结果,判断是否满足设定要求

2.选择InTime默认配方进行设定策略,运行编译

3.判定运行结果,满足时序要求跳转到 ,不满足跳转到5

4.依据当前运行结果与数据中心,机器学习引擎重新进行优化种子分配,写入综合编译策略,跳转到3.

5.综合优化结束,查看分析结果,并导出工程。

InTime策略优化选择的过程中,不能自动进行Recipe的切换。优化过程会一直沿用某个选定的Recipe持续进行,可能导致算法无法得到最终的目标时序。InTime的Recipe需要依据当前运行状态和所得到的结果数,人为进行切换。

InTime Recipe选择依据如下:

1)初始阶段选择:Intime default->工程首次优化校正、种子探索、优化

2)收敛阶段选择:Explorer-> Intime default无法得到目标时序时,需要在Intime default策略的运行结果中,选择最优结果作为子版本,进行探索。Deep dive->运行结果150个以上未能出现时,选择该策略进行深度策略分析,分析不同结果之间的策略差异

3)末端阶段选择:ExtraOpt explorer/placement explorer->应对综合阶段或者布局布线阶段进行优化探索。

InTime使用流程

1.设置优化目标、运行参数

常用参数设置包括:

1)TNS:时序优化目标

2)Runs per round:每个子版本运行次数

3)Maximum Runtime:每次运行最大消耗时间,超出该消耗时间,则终止该次运行

2.选择Recipe运行优化

Strat Recipe进行时序优化,软件开始自动设置优化策略,调用相应的综合器综合编译,布局布线。

运行结果以Job ID进行区分,并以层次结构逐级呈现。目标时序击中后,停止优化流程。

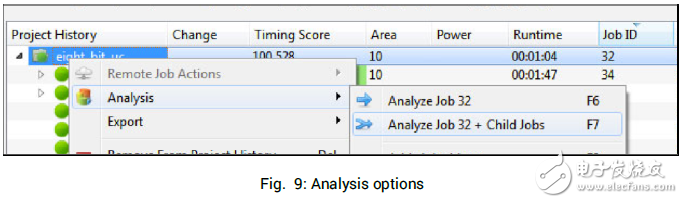

3.分析选择优化结果

InTime自动导出时序、面积、能耗等评估参数,用户可综合考虑各种参数,并选择所需要的最佳结果进行细致分析。

选择其中某个运行结果分析,得到优化数据与收敛曲线等。

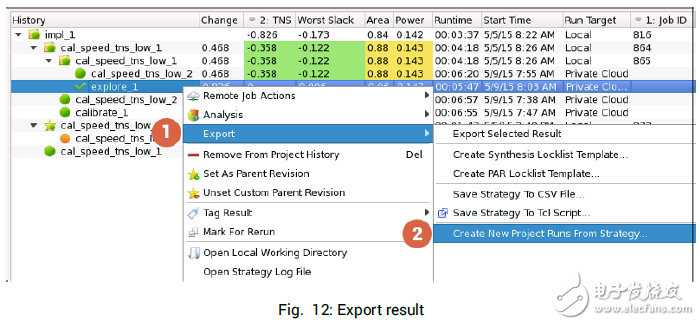

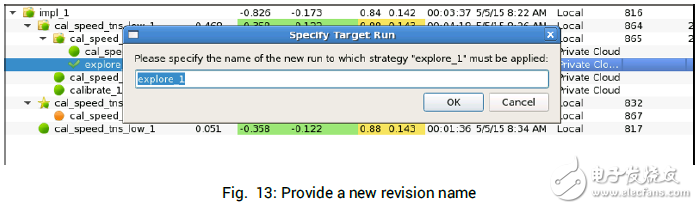

4. 工程导出

InTime最终需要导出某个击中目标时序的优化策略选择工程,用户可通过再次编译导出工程,验证时序是否满足要求。

四、工程验证

工程1

工程1芯片采用xc7a50t,系统时钟156M,目标时序TNS=0,LUT使用率在80%左右,内含SERDES、MAC等IP,其具体资源利用率如下图所示:

工程1项目加入较多信号观测的chipscope后,时序无法达到要求,TNS=-1.881存在风险。采用InTime进行时序自动优化。采用InTime Default配方进行策略探索,如图所示经两三轮的运行后,即击中目标时序,TNS=0。

VXLAN_S57H项目相对需要优化的目标较为简单,容易满足。且工程量较小,整体综合编译布局布线周期较短,无法有力说明InTime带来的优化便利性。

工程2

工程2器件采用xcku095,工程庞大,Vivado正常综合编译消耗时间在7小时左右。系统时钟在200M,内含多个SERDES、MAC、DDR IP核,时序目标在TNS=0。其具体资源利用率如下图所示:

最初工程TNS=-5982.01,首次策略选择InTimeDefault

经过多轮运行无法满足目标时序,在运行结果中选择最佳结果,设定为子版本。

将配方选择为Explorer,再次进行时序优化,得到目标时序TNS=0

五、InTime评估总结

InTime软件旨在不修改工程代码的情况下,不需要较多人为参与条件下,自动实现综合器时序优化选项的填写,运行达到目标时序。通过软件文档查看、原理分析、工程试验,可有效的说明,InTime具备使用简易、策略选择精确度高,最终获得良好的时序优化结果。且整个时序优化过程,人为参与极少。采用InTime软件即使投入非工程研发人员,也可实现时序优化。有助于工程开发效率的提高,缩短开发周期。

不错的 资料,学习一下,,,

wow,好详细的报告!是不是六百刀的折扣券?

这评测有点专业了

听lz这么一介绍感觉这个软件还是不错的

感觉给FPGA的工程师会带来便利 时序优化是个头疼的问题

这个厉害了紫薯布丁

△:

功能挺强大的软件!