在Quartus II 13.1里编完程序,查看RTL电路时发现,变量的值与程序里写的高低位反了,怎么回事?大神,求指点!

时间:10-02

整理:3721RD

点击:

在Quartus II 13.1里编完计数器的程序,查看RTL电路时发现,变量的值与程序里写的高低位反了,怎么回事?大神,求指点!

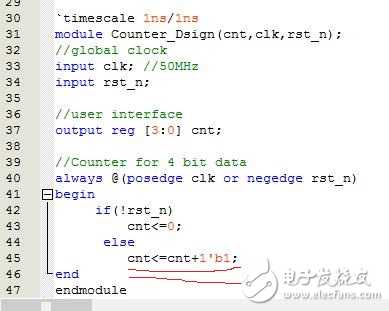

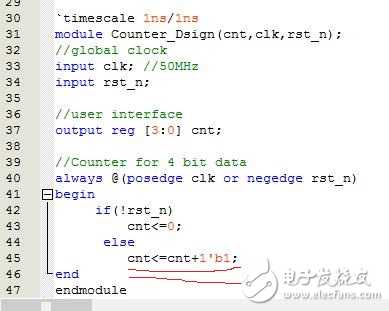

程序和RTL电路如下:

程序里写计数器自加1,在RTL电路里怎么变成了自加8了?高低位反了?

程序和RTL电路如下:

程序里写计数器自加1,在RTL电路里怎么变成了自加8了?高低位反了?

已解决。研究发现B[3..0]只是一个选择信号,并不是cnt要加的数,把cnt[0]~reg[3..0]展开发现,B[3..0]的4'h8只是选择cnt的第0位加1。

已解决。研究发现B[3..0]只是一个选择信号,并不是cnt要加的数,把cnt[0]~reg[3..0]展开发现,B[3..0]的4'h8只是选择cnt的第0位加1