verilog设计等精度频率计过程中遇到的计数问题

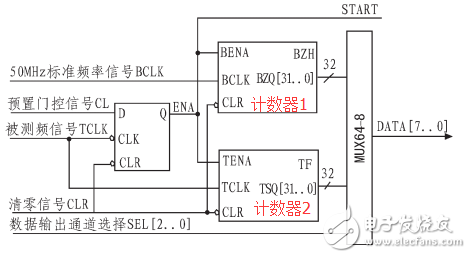

这个是等精度测频的原理图,闸门信号有效时,当被测信号上升沿来时,两个计数器分别对被测信号和标准时钟信号进行计数,但是现在问题是,怎么控制这两个计数器同时开始计数呢?如果用两个always的话,计数器2可以用

always @(posedge fx or negedge clr) //带清零和使能的计数器

begin

if(!clr) counter2 <= 32'b0; //异步复位

else if(Gate) counter2 <= counter2 + 1'b1

else counter2 <= counter2;

但是计数器1,也就是对标准信号的计数,怎么编程实现呢,如果用always的话,always @(posedge fx or negedge clr) ,因为它开始计数的时间就是被测信号上升沿来,门控有效时,但是它是clk来一个它计一个数,着怎么弄呢?

谢谢小编,现在下载学习。

小编电赛吧,metoo,我看别的资料,应该是把闸门信号来作为触发

奥,不是的,你是电赛的啊,是一个课程设计,

不懂帮顶,加油啊

不懂帮顶,加油啊

always @(posedge fclk or negedge clr) //带清零和使能的计数器

begin

if(!clr) counter1 <= 32'b0; //异步复位

else if(Gate) counter1 <= counter1 + 1'b1

else counter1<= counter1;

fclk为标准的信号

这样应该可以吧

围观一下

module cnt10(clk,rst,ena,outy,cout);

input clk,rst,ena;

output reg [3:0] outy;

output cout;

always @(posedge clk or posedge rst )

begin

if(rst) outy='b0000;

else if(ena)

begin

if (outy<'b1001) outy=outy+1;

else outy='b0000;

end

end

assign cout=outy[3] & outy[0];

endmodule

直接用标准信号做敏感事件呗。憋学死了。