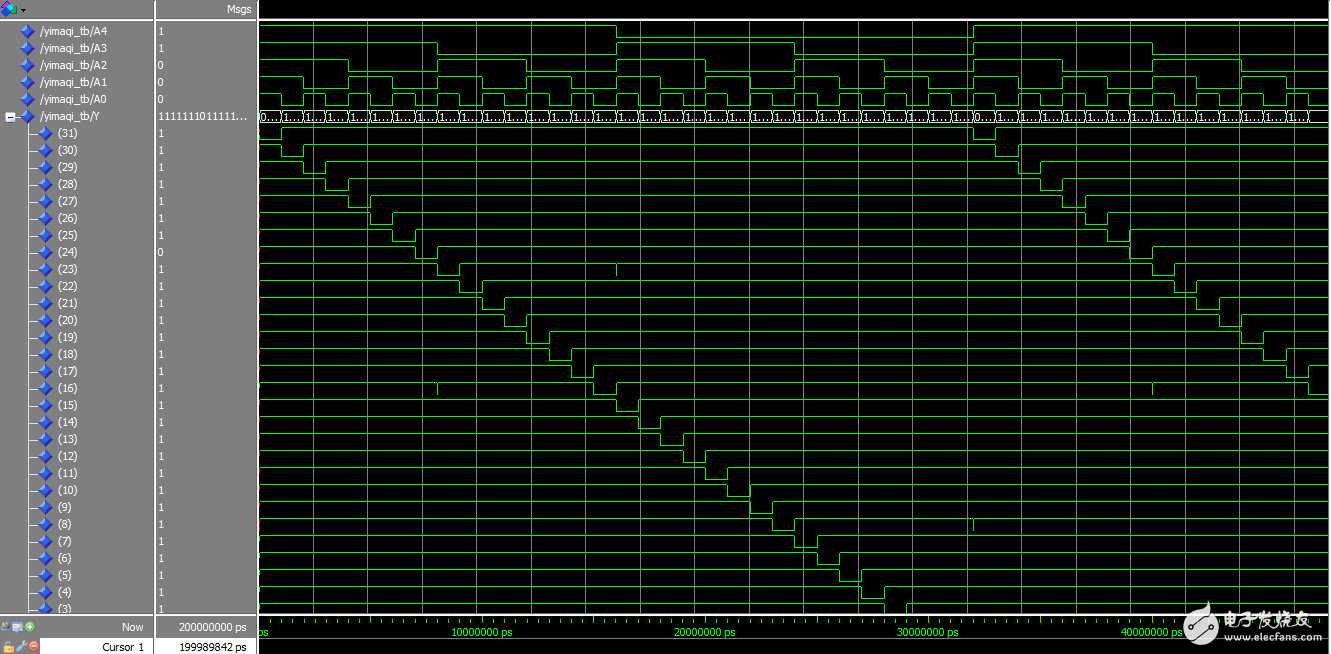

用VHDL写的5-32译码器进行功能仿真,波形竟然出现了毛刺,这是什么原因,求大神指导

时间:10-02

整理:3721RD

点击:

程序:

entity yimaqi is

port(A4,A3,A2,A1,A0:in bit;

Y:out bit_vector(31 downto 0));

end yimaqi;

architecture rtl of yimaqi is

signal A:bit_vector(4 downto 0);

begin

A<=A4&A3&A2&A1&A0;

Y<="11111111111111111111111111111110" when A="00000" else

"11111111111111111111111111111101" when A="00001" else

"11111111111111111111111111111011" when A="00010" else

"11111111111111111111111111110111" when A="00011" else

"11111111111111111111111111101111" when A="00100" else

"11111111111111111111111111011111" when A="00101" else

"11111111111111111111111110111111" when A="00110" else

"11111111111111111111111101111111" when A="00111" else

"11111111111111111111111011111111" when A="01000" else

"11111111111111111111110111111111" when A="01001" else

"11111111111111111111101111111111" when A="01010" else

"11111111111111111111011111111111" when A="01011" else

"11111111111111111110111111111111" when A="01100" else

"11111111111111111101111111111111" when A="01101" else

"11111111111111111011111111111111" when A="01110" else

"11111111111111110111111111111111" when A="01111" else

"11111111111111101111111111111111" when A="10000" else

"11111111111111011111111111111111" when A="10001" else

"11111111111110111111111111111111" when A="10010" else

"11111111111101111111111111111111" when A="10011" else

"11111111111011111111111111111111" when A="10100" else

"11111111110111111111111111111111" when A="10101" else

"11111111101111111111111111111111" when A="10110" else

"11111111011111111111111111111111" when A="10111" else

"11111110111111111111111111111111" when A="11000" else

"11111101111111111111111111111111" when A="11001" else

"11111011111111111111111111111111" when A="11010" else

"11110111111111111111111111111111" when A="11011" else

"11101111111111111111111111111111" when A="11100" else

"11011111111111111111111111111111" when A="11101" else

"10111111111111111111111111111111" when A="11110" else

"01111111111111111111111111111111" when A="11111" else

"11111111111111111111111111111111";

end architecture rtl;

用这个方法写的2-4译码器没有问题

在百度知道上看有人说组合逻辑电路是很容易出毛刺的,要想没有毛刺就要写时序逻辑电路,不知道是不是这样,还有我进行的是功能仿真啊!结果应该很理想啊。求大神们解惑

谢谢大家啦

entity yimaqi is

port(A4,A3,A2,A1,A0:in bit;

Y:out bit_vector(31 downto 0));

end yimaqi;

architecture rtl of yimaqi is

signal A:bit_vector(4 downto 0);

begin

A<=A4&A3&A2&A1&A0;

Y<="11111111111111111111111111111110" when A="00000" else

"11111111111111111111111111111101" when A="00001" else

"11111111111111111111111111111011" when A="00010" else

"11111111111111111111111111110111" when A="00011" else

"11111111111111111111111111101111" when A="00100" else

"11111111111111111111111111011111" when A="00101" else

"11111111111111111111111110111111" when A="00110" else

"11111111111111111111111101111111" when A="00111" else

"11111111111111111111111011111111" when A="01000" else

"11111111111111111111110111111111" when A="01001" else

"11111111111111111111101111111111" when A="01010" else

"11111111111111111111011111111111" when A="01011" else

"11111111111111111110111111111111" when A="01100" else

"11111111111111111101111111111111" when A="01101" else

"11111111111111111011111111111111" when A="01110" else

"11111111111111110111111111111111" when A="01111" else

"11111111111111101111111111111111" when A="10000" else

"11111111111111011111111111111111" when A="10001" else

"11111111111110111111111111111111" when A="10010" else

"11111111111101111111111111111111" when A="10011" else

"11111111111011111111111111111111" when A="10100" else

"11111111110111111111111111111111" when A="10101" else

"11111111101111111111111111111111" when A="10110" else

"11111111011111111111111111111111" when A="10111" else

"11111110111111111111111111111111" when A="11000" else

"11111101111111111111111111111111" when A="11001" else

"11111011111111111111111111111111" when A="11010" else

"11110111111111111111111111111111" when A="11011" else

"11101111111111111111111111111111" when A="11100" else

"11011111111111111111111111111111" when A="11101" else

"10111111111111111111111111111111" when A="11110" else

"01111111111111111111111111111111" when A="11111" else

"11111111111111111111111111111111";

end architecture rtl;

用这个方法写的2-4译码器没有问题

在百度知道上看有人说组合逻辑电路是很容易出毛刺的,要想没有毛刺就要写时序逻辑电路,不知道是不是这样,还有我进行的是功能仿真啊!结果应该很理想啊。求大神们解惑

谢谢大家啦

功能仿真结果,有毛刺

建议用时钟沿进行同步

我到底错哪了,有没有人指正一下啊

嗯,谢谢啦