6748设备时钟(3)

这个帖子主要说说查看时钟输出时遇到的问题以及解决方法。

问题1:在查看PLL0时钟时,当OCSEL配置为17h时,理论值SYSCLK1=456/1=456MHz;实际观察为:20~98kHz变动,显然不符合要求。

原因:SYSCLK1是系统主时钟,456MHz,而我的示波器带宽为100MHz,示波器带宽不够。

解决方法:将PLL0的OSCdiv寄存器分频因子改为2,进行降频输出来测量。那么在测量SYSCLK1时,示波器就会测到456MHz/(2+1)=152MHz的信号,实际测试到的是151.997MHz。测量结果如下:

问题2:用示波器观察PLL1的时钟SYSCLK1、SYSCLK2、SYSCLK3,没有得到正确的显示结果。

原因:在配置寄存器的过程中,没有使能CKEN寄存器。6748技术参考手册中有写:ForPLLC1 OBSCLK to toggle, both the OD1EN bit and the OBSEN bit in the PLLC1 clockenable control register (CKEN) must be set to 1。我因为没有使能CKEN寄存器中的OBSEN位,所以无法正常输出。

测试过程如下:

1)、理论上,由GEL文件初始化后时钟为:

PLL1_SYSCLK1=312MH;PLL1_SYSCLK2=156MHz;PLL1_SYSCLK3=104MHz。

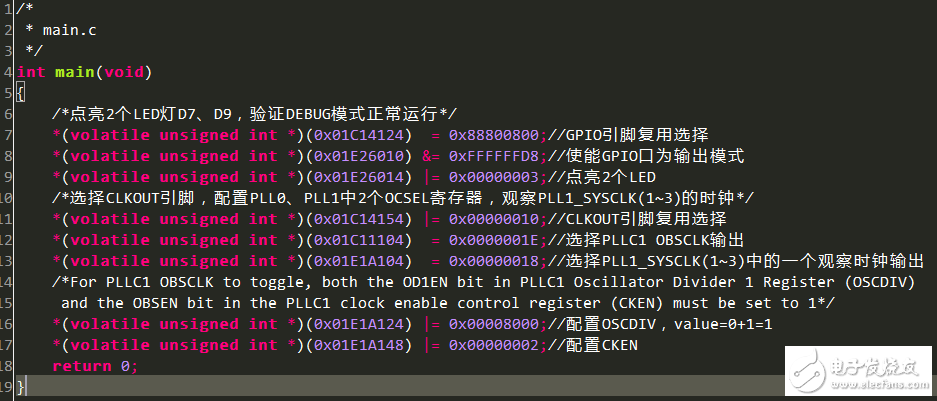

2)、程序如下:

3)、测试结果:

PLL1_SYSCLK1:理论值SYSCLK1=312MHz,实际观察为:311.993MHz,符合要求。

PLL1_SYSCLK2:理论值SYSCLK2=156MHz,实际观察为:155.996MHz,符合要求。

PLL1_SYSCLK3:理论值SYSCLK3=104MHz,实际观察为:103.998MHz,符合要求。

特别感谢#电子微创意# !

谢谢你帮助我解答这些问题,再次表示感谢!

祝大家圣诞快乐!

@电子微创意 不愧是DSP负责人

希望我们这里的问题越来越深入,期望更多的网友来分享交流。感谢发烧友论坛和创龙电子提供的平台。

都是学习,多交流分享。现在的问题就是将来的经验。