6748设备时钟(2)

承接6748设备时钟介绍,接下来报告用示波器观察到的SYSCLKn的时钟频率。

1、PLL总框图还是要贴上来的,所有的配置都根据总框图来进行。

还有仿真过程:

2、直接阅读创龙的GEL文件可以知道PLL0_SYSCLK(1~7)和PLL1_SYSCLK(1~3)的配置情况。简单贴一点删减了的代码,具体程序阅读创龙的GEL文件即可,这里的代码只做示意之用。

Set_Core_456MHz() {

device_PLL0(0,18,0,0,1,3,9);

}

Set_DDRPLL_156MHz() {

device_PLL1(12,0,0,1,2);

}

Set_DDR2_156MHz() {

Set_DDRPLL_156MHz();

DEVICE_DDRConfig();

}

Core_456MHz_DDR2_156MHz() {

Set_Core_456MHz();

Set_DDR2_156MHz();

}

device_PLL0(unsigned int CLKMODE, unsigned intPLLM, unsigned int POSTdiv,unsigned int PLLdiv1, unsigned int PLLdiv2, unsignedint PLLdiv3, unsigned int PLLdiv7 ) {

}

device_PLL1(unsigned int PLLM,unsigned intPOSTdiv,unsigned int PLLdiv1, unsigned int PLLdiv2, unsigned int PLLdiv3 ) {

}

从程序可以知道PLL0的配置情况如下:

1)、外部有源晶振:24MHz;

2)、CLKMODE=0;PLLM=18; POSTdiv=0; PLLdiv1=0; PLLdiv2=1; PLLdiv3 =3;PLLdiv7=9。

阅读6748技术参考手册可以知道:

24*(18+1)=456 MHz;456/1=456 MHz;

SYSCLK1=456/1=456 MHz;SYSCLK2=456/2=228 MHz;

SYSCLK3=456/4=114MHz;SYSCLK7=456/1=45.6 MHz;

同理,PLL1的配置情况如下:

1)、外部有源晶振:24MHz;

2)、PLLM=12; POSTdiv=0; PLLdiv1=0; PLLdiv2=1; PLLdiv3 =2。

阅读6748技术参考手册可以知道:

24*(12+1)=312MHz;312/1=312 MHz;

SYSCLK1=312/1=312 MHz;SYSCLK2=312/2=156 MHz;

SYSCLK3=312/3=104MHz。

3、使用读取内存的方式配置寄存器,从而查看各模块时钟。

PLL0时钟查看分如下几步:

1)、点亮2个LED灯D7、D9,验证DEBUG模式正常运行;

2)、CLKOUT引脚复用选择;

3)、选择PLL0_SYSCLK(1~7)中的一个,在CLKOUT引脚观察输出。

具体代码如下:

4、用示波器观察输出。

CLKOUT引脚位于C4748底板扩展口J3-pin11(up_OBSCLK);

接地线我连的J3-pin15(GND)。

由下图配置寄存器,选择输出时钟:

先上开发板上点亮D7、D9的图。注意只有2个LED亮了,只是太亮感觉4个都亮了。

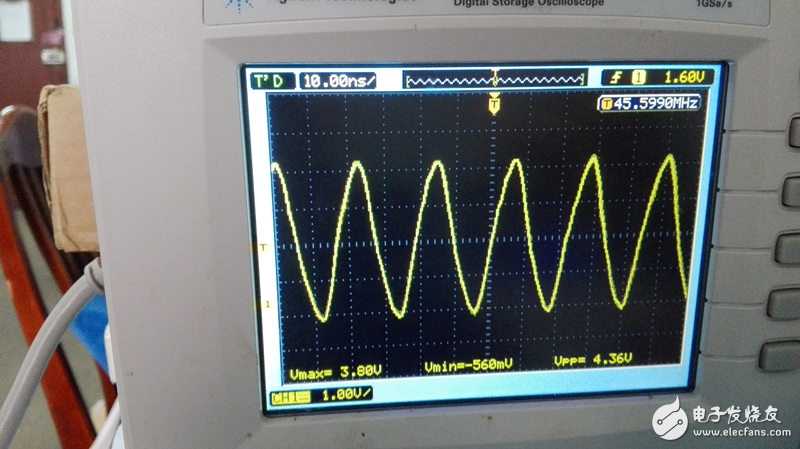

1)、当OCSEL配置为1Dh时,理论值SYSCLK7=456/1=45.6 MHz,实际观察为:45.599MHz,符合要求。

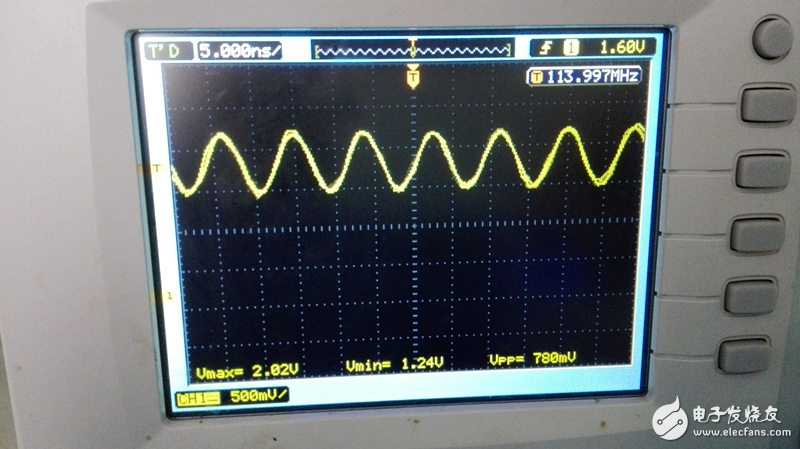

2)当OCSEL配置为19h时,理论值SYSCLK3=456/4=114MHz;实际观察为:113.997MHz,符合要求。

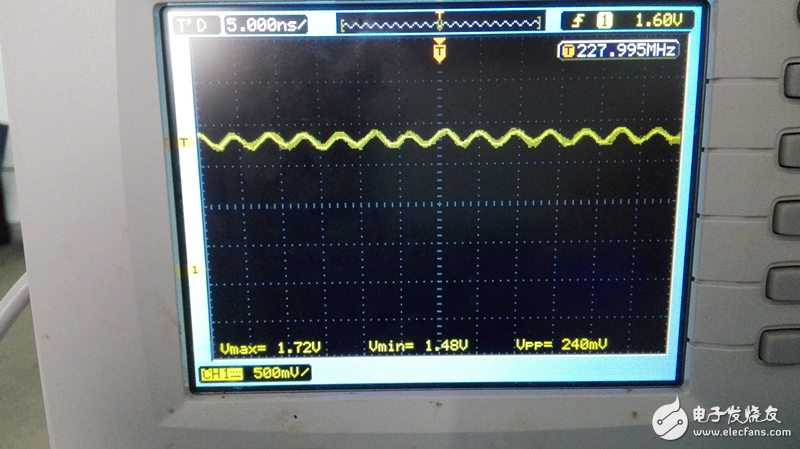

3)当OCSEL配置为18h时,理论值SYSCLK2=456/2=228 MHz;实际观察为:227.995MHz,符合要求。

4)当OCSEL配置为17h时,理论值SYSCLK1=456/1=456 MHz;实际观察为:20~98kHz变动,显然不符合要求。

5、另外,用示波器观察PLL1的时钟SYSCLK1、SYSCLK2、SYSCLK3,没有得到正确的显示结果。所以这一部分我还要继续查找原因。

这是观察PLL1时钟的配置,各位可以帮我看看有什么错误?帮忙分析原因!

未完,待续……

有点复杂呐

问题1:SYSCLK1是系统主时钟,456MHz,测量工具得给力才行。你100MHz带宽的示波器我觉得还是不行的。你可以了解一下示波器的使用方面的知识。正好发烧友论坛有篇不错的文章:http://www.elecfans.com/article/85/126/2012/20120214260151.html

问题2:PLL1的时钟也可以输出测量,测试方法与PLL0相同。

你所谓测不到是因为示波器带宽不够,可以通过修改寄存器:OSCdiv进行降频输出来测量。例如PLL0的OSCdiv寄存器分频因子为3,那么在测量SYSCLK1时,示波器就会测到456MHz/(3+1)=114MHz的信号,建议采用交流耦合。

好的!多谢!这就去看看。

这个建议好,我马上试试,回头反馈效果哈

按照你的方法做了,将PLL0的OSCdiv寄存器分频因子改为2,那么在测量SYSCLK1时,示波器就会测到456MHz/(2+1)=152MHz的信号,实际测试到的是151.997152MHz。多谢!

所以,原因应该就是示波器带宽不够。新技能get!