+ 6748设备时钟介绍

1、首先先介绍一下DSP的PLL。下面的解释虽然不是官方文档直译,但是我认为解释的非常清楚。特贴出来跟大家共享!

PLL锁相控制环路是一种反馈控制电路,简称锁相环。锁相环利用外部输入的参考信号控制环路内部振荡信号的频率和相位,可以实现输出信号频率对输入信号频率的自动跟踪,从而使信号稳定。DSP片内一般都集成了PLL硬件电路,该电路专门用于时钟信号,PLL将原始的可能不稳定的时钟结果锁定,输出稳定可靠的时钟,提供给DSP内部的各个硬件单元,从而保证这些硬件单元对时钟的要求。一般低级的DSP芯片PLL电路简单,高级的DSP芯片(如C674x、C6455、C66系列)由于内部集成很多对时钟要求很高的硬件单元,如网口、PCIE接口和RapidIO接口等,所以其PLL电路就比较复杂,一般有2个以上的PLL电路。

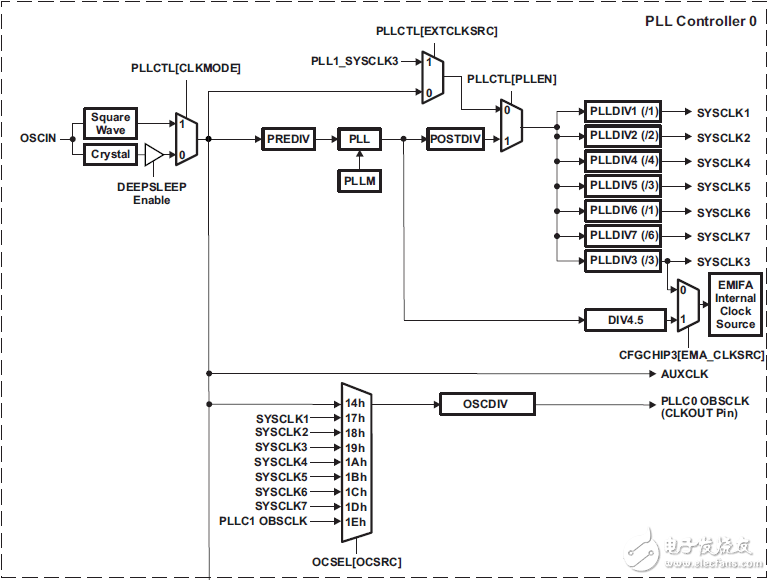

C6748DSP的PLL结构如下:

图中PLLCTL[CLKMODE]用于选择时钟源的波形,如果时钟源OSCIN为方波,选择1;如果为正弦波,选择0。选择后的时钟可以直接从AUXCLK引脚上看到。CIN信号实际上仍然直接到达PREdiv进行预分频,预分频后得到慢速的时钟,然后到PLL单元进行倍频。倍频后的信号,根据需要再进行后分频,得到需要的运行时钟。这个基准时钟分别送到多个分频器(1~7),并进一步分配到DSP内部的各个硬件单元。为了更加方便与外设通信,DSP的EMIFA接口还可以直接从PLL模块经过固定的4.5倍分频得到时钟信号,提供还模块读写数据。以下是DSP内部各个硬件的时钟来源:

2、PLL设置

根据PLL的状态不同,其设置方法也有所差别。PLL的设置可看考英文版6748技术参考手册以及创龙翻译的《TMS320C6748 DSP设备时钟》,这里我就不再搬运资料了。代码直接参考创龙提供的GEL文件:Tronlong_C6748.gel;直接看代码就能知道怎样设置各个寄存器的值,从而设置所需频率。从引脚PLLC0 OBSCLK(CLKOUT Pin)就可方便的观察所设置的频率值。

接下来我会实际调试,并用示波器显示各部分得到的频率值。主要调试观察的模块为:USB时钟、DDR2/mDDR 存储控制器时钟、EMIFA 时钟、McASP 时钟、McBSP 时钟等。

该是他们排上用场的时候了!

未完,待续……

设备很是齐全嘛

就是人太水了一点。哈哈哈

!

您好,我现在需要用CLKOUT引脚输出各个 时钟,我在gel文件中配置如下

PLL0_OSCdiv1 &= 0;

PLL0_OSCdiv1 |= 0; //1分频

PLL0_OCSEL & = 0;

PLL0_OCSEL | = 0x19; //PLL0_SYSCLK3 的时钟

PLL0_OSCdiv1 |=(0x00008000); // 使能了OSCdiv[OD1EN]

同时,

其中CKEN[OBSEN]位是默认使能的。但是我在CLKOUT引脚中并没有输出,

不知道我上边的配置是否成功? 还需要其他设置吗?