SI-listAllegro Sigrity OptimizePI Training(一)去耦电容仿真设置

SI-list【中国】Allegro Sigrity OptimizePI Training(一)去耦电容仿真设置

2016-07-26 李黎明 shark4685

本文大纲

1. 去耦电容仿真设置(一)

2. 去耦电容仿真设置(二)

3. 去耦电容仿真设置(三)

4.仿真优化结果查看

去耦电容的优化需要综合考虑PDN的性能和成本因素,在目前的PCB或封装设计中,往往存在PDN电源噪声(包括低频和高频)超标、性能不满足设计、成本较高等问题。随着设计变得越来越复杂,电容的位置和容值选择往往大大超出设计人员的经验。

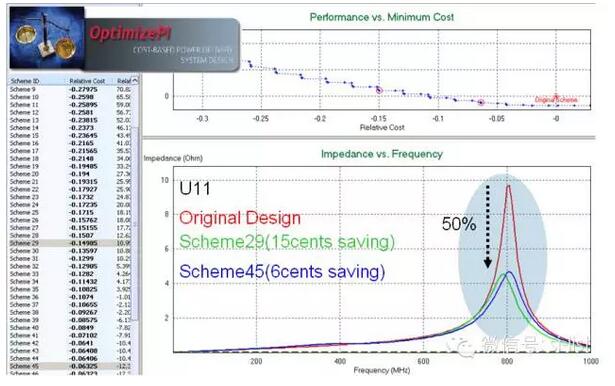

OptimizePI提供业界第一个能够综合考虑电源PDN性能和成本的解决方案。OptimizePI使用专利的电磁分析和优化算法,可以快速、准确地进行电源分析,自动排列组合去耦电容的容值和位置,提供兼顾性能和成本的电容优化方案,根据优化的不同目标,帮助设计人员在成本、空间、数量和性能之间做出权衡。OptimizePI提供交互式的优化结果后处理,方便用户直观地选择优化结果

去耦电容仿真设置(一)

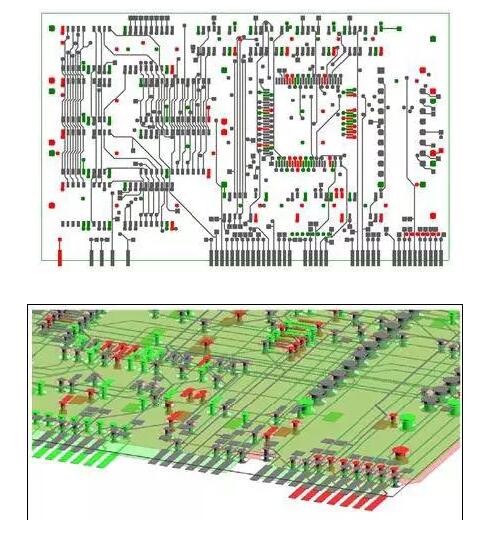

本模块用到的PCB案例:

1. 6层PCB设计,第2层是地平面、第5层是电源平面

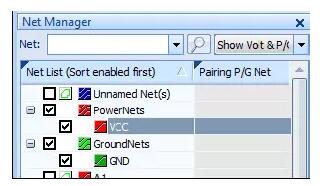

2. 1个电源网络:VCC(红色显示网络)

3. 1个地网络:GND(绿色显示网络)

4. 1个VRM、5个IC器件(阻抗观测点)、28个去耦电容

本模块中,我们将会用OptimizePI分析不同的电容滤波方案对几个IC器件的电源阻抗的影响,从OptimizePI推荐的方案中选择合适的方案优化PDN设计。

1. 开始菜单->Cadence->Sigrity 2015->Sigrity Suite Manager。

2. 选择OptimizePI,在右边窗口选择可用的license双击启动OptimizePI。

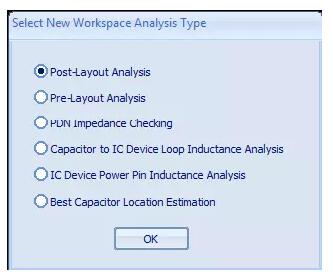

3. 在菜单栏选择Workspace->New,在弹出的窗口中,选择“Post-Layout Analysis”,点击OK确认。

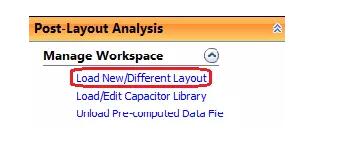

4. 在workflow中选择“Load New/Different Layout”,在弹出的对话框选择“Load an existing layout”,打开“D:\Training\Sigrity_OptimizePI\Lab\Module1\demo_OPI.spd”。

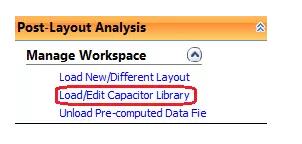

5. 在workflow中选择“Load/Edit Capacitor Library”

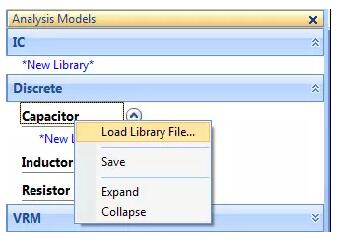

在弹出的Analysis Model Manager窗口,在Discrete-Capacitor位置,右键菜单选择“Load Library File”,打开“D:\Training\Sigrity_OptimizePI\Lab\Module1\demo_decap_library.xml”。

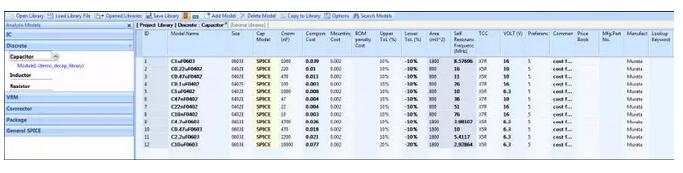

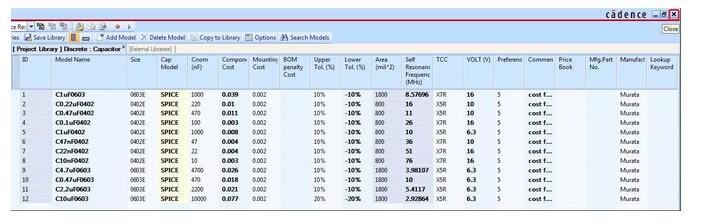

导入的电容库如下:

6. 点击Analysis Model Manager窗口右上角的![]()

7. 在workflow中选择“Check Stackup”,打开Stack Up窗口。检查并设置金属层、介质层的厚度和材料参数。设置完成后点击OK按钮回到主界面。

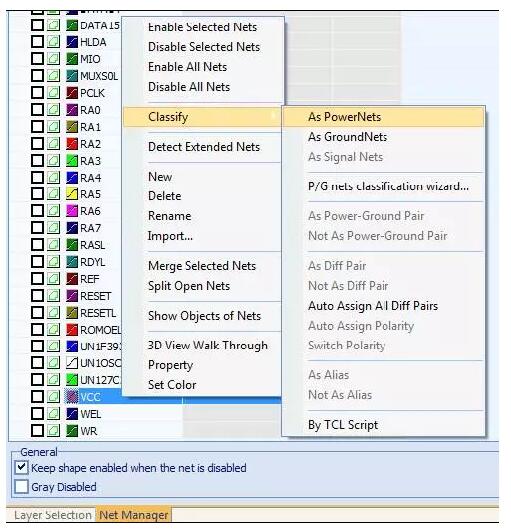

8. 在workflow中选择“Select Nets”。在Net Manager页面,选择VCC网络,右键菜单选择Classify->As PowerNets,然后使能VCC网络。

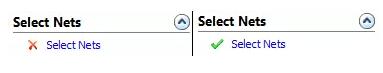

注意使能VCC网络后,Workflow的Select Nets前面的图标![]()

-----本节完,共四章----

关于SI-list【中国】微信群

本群专注于:高速链路设计,信号完整性,电源完整性仿真,测试,验证相关技术交流,经验分享,解疑答惑,如方便,可把单位,研究方向在群名称表示出,方便大家交流合作,如果消息太多设置为免打扰模式,不便的可退群。

注明加SI-list【中国】微信群.

例子文件呢?

好东西,不过是不是介绍的太简单了!

謝謝分享

谢谢分享!

谢谢分享!

谢谢分享!

相當重要的一環!

例子文件呢?

感謝分享~

感謝分享~

例子在哪里下载啊?

感谢分享!

感谢分享