SI-list测量时钟时Period Jitter、Cycle-Cycle 与 TIE这三种方式该如何选择?

SI-list【中国】测量时钟时Period Jitter、Cycle-Cycle 与 TIE这三种方式该如何选择?

2016-06-13 SI-list【中国】shark4685

最近遇到到时钟测量部分的问题,现实中的时钟会有Jitter的问题,包括Random jitter和deterministic Jitter,而在deterministic jitter下面有一部分是由于时钟周期不稳定引起的jitter,姑且称之为PeriodJitter。

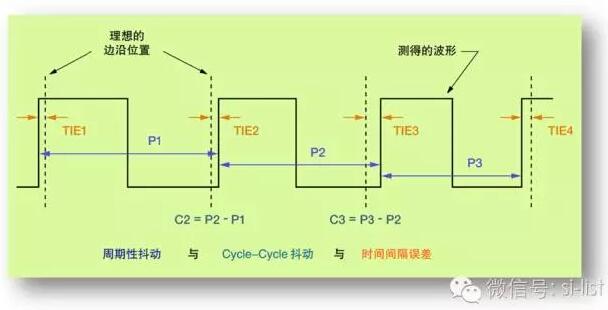

而对这部分Jitter的测量有三种标准测试,Period Jitter、Cycle-Cycle and TIE,下方图片是这三种测量方式的定义,问题就是这三种方式该如何选择。换言之,这三种方式分别适用于什么情况。

首先指出题主的一个错误,就是deterministic jitter下分解到是周期性抖动即periodic jitter,而不是periodjitter,period jitter是实际时钟总抖动的一种表示方式。下面看一张图(画工较为随意)

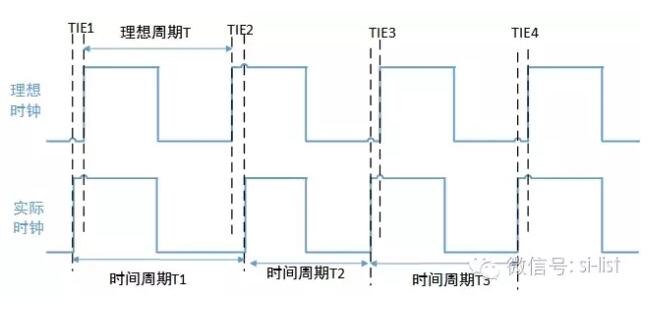

任何一个时钟信号不可能是理想的,受到干扰和随机噪声影响,实际周期总会变化,上图给出了一个示意图(仅考虑上升沿的偏差,对于RGMII和DDR这种双边沿采样的系统,下降沿也要考虑)

时钟的总抖动(total jitter)有3种统计方式

1.时间间隔误差(TIE jitter)

即统计,每一个实际时钟的边沿与理想时钟的边沿之间的偏差(考虑正偏还是负偏)

TIE jitter实际上是Period jitter累积的结果

2.周期抖动(Period jitter)

即统计,每一个实际时钟的周期(也就是上升沿到上升沿)与理想时钟周期之间的偏差。

也就是Period jitter = T1- T,实际也就是TIE2-TIE1

也就是说,在数学上,Period jitter是TIE jitter的差分

3.相邻周期抖动(Cycle to Cycle jitter)

即统计,实际时钟的当前周期与实际时钟的上一个周期之间的偏差

也就是Cycle to Cycle jitter = T2 -T1

也就是说,在数学上,Cycle to Cycle jitter 是Period jitter的差分

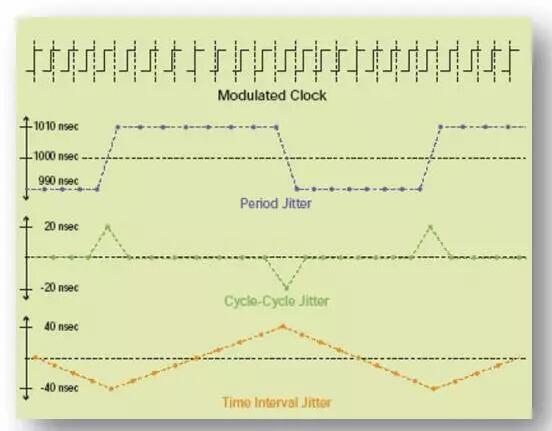

一般高速示波器测量时钟的时候都会统计3种时钟的总抖动。这三种抖动都是描述时钟的总抖动,有点像位移、速度、加速度的关系(都是描述物体的运动),应用的场合不太一样。下面举例说明一下。

Period Jitter

高速并行数据通信系统,通常发送端会在时钟上升沿的时候向发送数据,然后将时钟加一个固定延时后发送给接收端(或接收端内部加延时),接收端在时钟上升沿采样数据。

数据的发送和采样用的是时钟的同一个边沿,是对齐的,每个数据的持续时间就是实际时钟的当前周期,采样的时序关系(建立时间与保持时间)只受实际时钟的当前周期影响。上一次的周期偏差(Period jitter)不会影响到这一次的时序关系,既不会存在Period jitter的累积,即无需关注TIE抖动。

TIE Jitter

在高速串行数据通信,一般都是嵌入式时钟系统,即不单独提供时钟信号,接收端通过CDR从数据中恢复出时钟用于采样。发送端发送数据的时候,根据自己的参考时钟的边沿,连续不断的发送数据。接收端恢复出时钟后,利用该时钟采样连续不断的数据,当前时钟边沿与当前数据边沿要满足一定的时序关系。由于恢复时钟的机制,数据发送和采样做不到用同一个时钟边沿,那么时序关系就受每一次的周期偏差的影响,既存在Period jitter的累积,需要关注TIE抖动。

当然TIE会影响CDR和PLL的工作。

Cycle to Cycle Jitter

在扩频通信等需要扩频时钟(spread spectrum clock)的应用,由于频率本身就是变的,那么统计出的PeriodJitter就会很大不足已体现稳定性,这时统计Cycle to Cycle Jitter就有意义了。

以上算是时域的分析

——————————————————

统计域分析

题主所说的total jitter可以分解为Random jitter和Deterministic Jitter,这是通过统计分析做出的。

有空再补充

——————————————————

频域分析

示波器统计的total jitter,通常会通过傅里叶变换给出jitter的频域分布,这有利于我们定位干扰来自与哪里,如何滤波。

Jitter是时钟偏差的时域结果,而频域内就是相位噪声。Jitter就是相位噪声在频域的积分。

相位噪声分析对PLL十分重要,这决定了PLL能否产生低抖动时钟。

有空再补充。

关于SI-list【中国】微信群

本群专注于:高速链路设计,信号完整性,电源完整性仿真,测试,验证相关技术交流,经验分享,解疑答惑,如方便,可把单位,研究方向在群名称表示出,方便大家交流合作,如果消息太多设置为免打扰模式,不便的可退群。

注明加SI-list【中国】微信群.

谢谢小编!