SI-listAllegro Sigrity OptimizePI Training(三)去耦电容仿真设置

SI-list【中国】Allegro Sigrity OptimizePI Training(三)去耦电容仿真设置

原创 2016-07-27 李黎明 shark4685

本文大纲

1. 去耦电容仿真设置(一)

2. 去耦电容仿真设置(二)

3. 去耦电容仿真设置(三)

4.仿真优化结果查看

关于OptimizePI

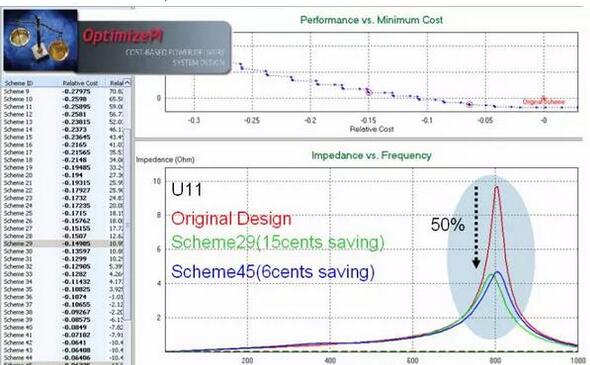

去耦电容的优化需要综合考虑PDN的性能和成本因素,在目前的PCB或封装设计中,往往存在PDN电源噪声(包括低频和高频)超标、性能不满足设计、成本较高等问题。随着设计变得越来越复杂,电容的位置和容值选择往往大大超出设计人员的经验。

OptimizePI提供业界第一个能够综合考虑电源PDN性能和成本的解决方案。OptimizePI使用专利的电磁分析和优化算法,可以快速、准确地进行电源分析,自动排列组合去耦电容的容值和位置,提供兼顾性能和成本的电容优化方案,根据优化的不同目标,帮助设计人员在成本、空间、数量和性能之间做出权衡。OptimizePI提供交互式的优化结果后处理,方便用户直观地选择优化结果

去耦电容仿真设置(三)

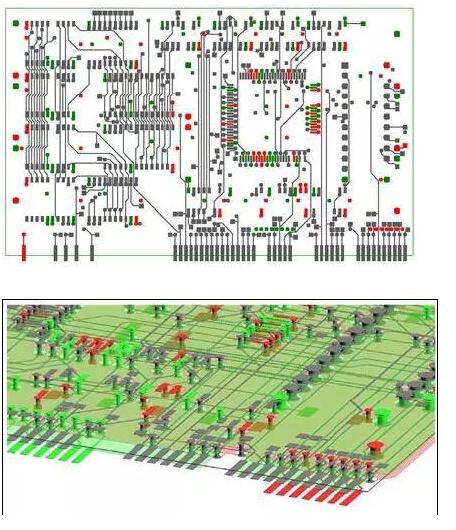

本模块用到的PCB案例:

1. 6层PCB设计,第2层是地平面、第5层是电源平面

2.1个电源网络:VCC(红色显示网络)

3.1个地网络:GND(绿色显示网络)

4.1个VRM、5个IC器件(阻抗观测点)、28个去耦电容

本模块中,我们将会用OptimizePI分析不同的电容滤波方案对几个IC器件的电源阻抗的影响,从OptimizePI推荐的方案中选择合适的方案优化PDN设计。

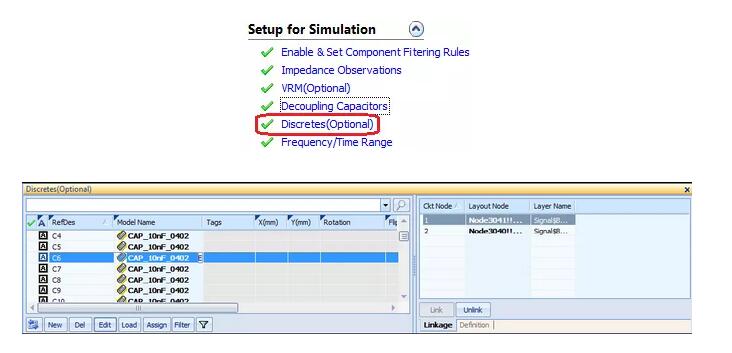

15. 在Workflow中选择“Discretes(Optional)”,这一步用于检查和设置如电感、磁珠、电阻等其它器件的模型。本案例中不需要设置

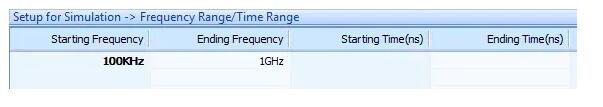

16. 在Workflow中选择“Frequency/Time Range”。

设置仿真频率为100KHz-1GHz。

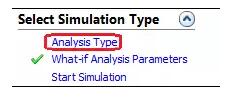

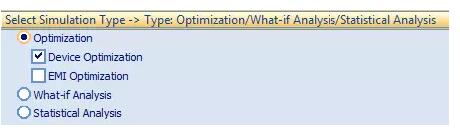

17. 在Workflow中选择“Analysis Type”。

选择Optimization->Device Optimization。点击OK确认

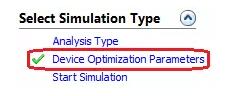

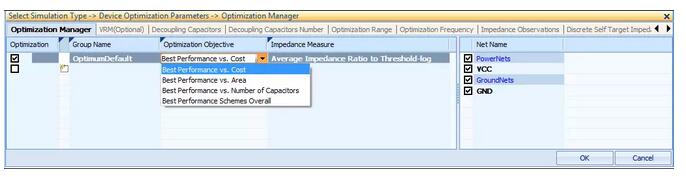

18. 在Workflow中选择“Device Optimization Parameters”。

在Device Optimization Parameters->Optimization Manager页面,设置优化目标为“Best Performance vs. Cost”,在优化PDN性能的同时尽可能降低电容成本。

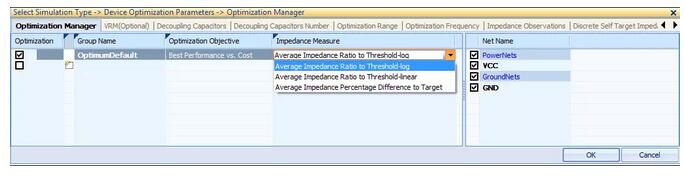

Impedance Measure用于设置PDN阻抗的测量方式:

“Average Impedance Ratio to Threshold-log” 是将仿真得到的每条阻抗曲线上每个频点的阻抗和Threshold曲线阻抗的差,取Log,再相加得到一个最终的PDN阻抗值;

“Average Impedance Ratio to Threshold-linear”是将仿真得到的每条阻抗曲线上每个频点的阻抗和Threshold曲线阻抗的差,直接相加得到一个最终的PDN阻抗值;

“Average Impedance Percentage Difference to Target”是将仿真得到的每条阻抗曲线上每个频点的阻抗和Target曲线阻抗的差的百分比相加得到一个最终的PDN阻抗值。

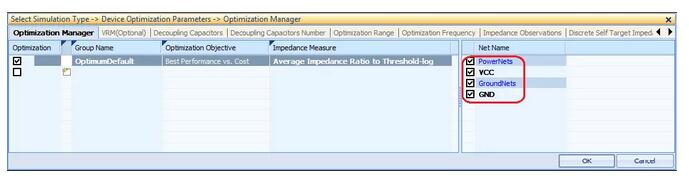

本案例选择默认的“Average Impedance Ratio to Threshold-log”。

右边的网络选择区域,勾选VCC和GND网络进行仿真。

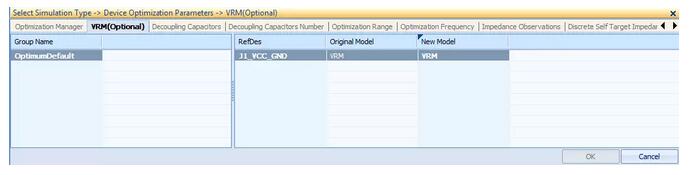

19. 在Device Optimization Parameters->VRM(Optional)页面,可以查看和修改VRM器件的模型。本案例不需要修改。

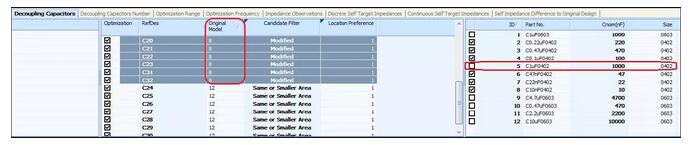

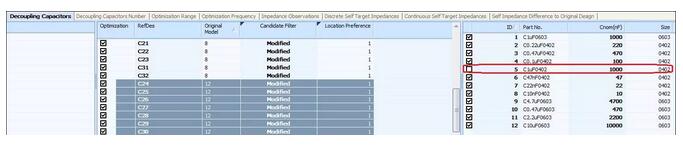

20. 在Device Optimization Parameters->Decoupling Capacitor页面,设置哪些电容需要考虑替换成其它电容,每个电容分别可以替换成哪些电容类型。

每个电容可以替换的候选电容类型,可以选择内置的相同封装、相同或更小封装、任意类型、相同器件这4种模式,默认方式是相同或更小封装,也可以手动在右边的候选电容区域直接勾选相应的电容类型。

选择所有ID为8的电容,在右边的候选电容列表中,把ID 5的C1uF0402电容取消掉。

选择所有ID为12的电容 ,在右边的候选电容列表中,把ID 5的C1uF0402电容取消掉。

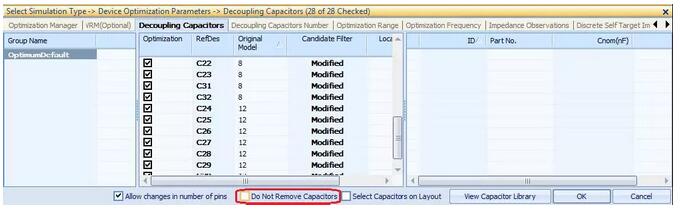

如果在仿真优化中不希望减少电容数量,可以把“Do Not Remove Capacitor”选项勾上。

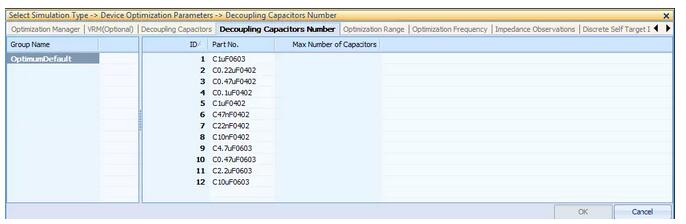

21. 在Device Optimization Parameters->Decoupling Capacitor Number页面,可以设置每种电容的最大数量。本例不需要设置。

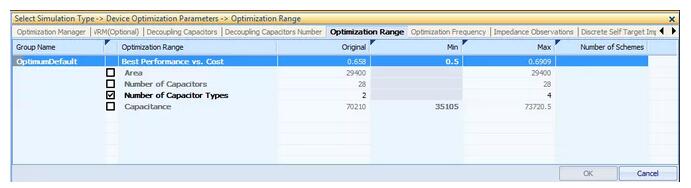

22. 在Device Optimization Parameters->Optimization Range页面,可以设置电容优化方案的其它约束,如电容成本范围、电容面积范围、电容种类最大值、电容数量最大值、总容值范围等。本案例使用如下设置。

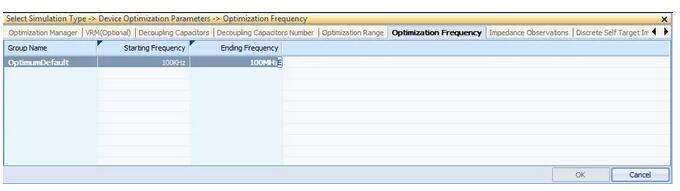

23. 在Device Optimization Parameters->Optimization Frequency页面,设置优化的频率范围。这个优化频率范围必须在前面设置的仿真频率的范围内。可以根据电源噪声频谱特点、电源阻抗特性等来合理设置优化频率范围。本案例设置优化范围为100KHz-100MHz。

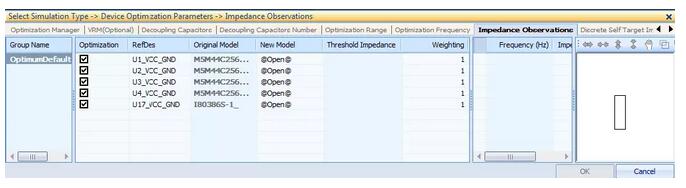

24. 在Device Optimization Parameters->Impedance Observations页面,可以设置每个阻抗观测点的Threshold Impedance曲线。没有设置Threshold Impedance的话,OptimizePI会根据Layout和滤波电容的情况,自动生成对应的Threshold Impedance。

还可以设置各阻抗观测点的权重,weighting数值越大的权重也越大。

本案例使用默认的设置,不做修改。

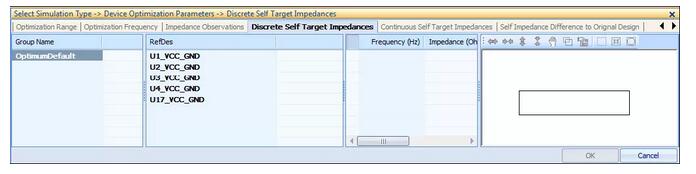

25. Device Optimization Parameters的其它几个页面,本案例中没有涉及到,保留默认设置就可以

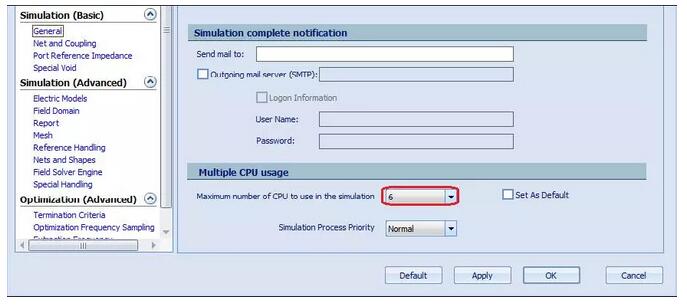

26. 在菜单栏选择Tools->Options->Edit Options,在Simulation(Basic)->General页面,设置仿真使用的CPU最大数量。

27. 在菜单栏选择Workspace->Layout File->Save,保存Layout修改。

28. 在菜单栏选择Workspace->Save,保存OptimizePI配置文件为demo.opix。

29. 在Workflow选择“Start Simulation”,开始仿真。

-----本节完,共四章----

关于SI-list【中国】微信群

本群专注于:高速链路设计,信号完整性,电源完整性仿真,测试,验证相关技术交流,经验分享,解疑答惑,如方便,可把单位,研究方向在群名称表示出,方便大家交流合作,如果消息太多设置为免打扰模式,不便的可退群。

注明加SI-list【中国】微信群.

謝謝分享

謝謝分享

谢谢分享!