SI-listpackage model的那些事儿(三)

SI-list【中国】package model的那些事儿(三)原创 2016-02-25 SI-list【中国】shark

本文大纲

1. [package] [pin] [package model]的爱恨情仇

2. [package model]的自述

3. 用hspice调用package参数的区别

3用hspice调用package参数的区别

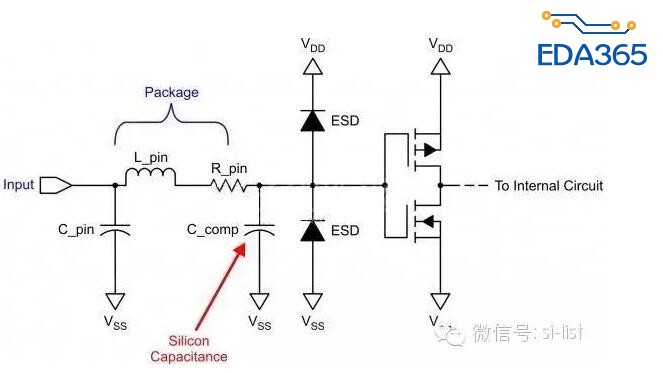

上面啰嗦了一大堆关于[package model],[package]和[pin]的相关知识,底下咱们就得学以致用了。对于用来说当然是仿真软件如何调用了,首先我们先来看下[package]和[pin]字段参数调用,因为[package]和[pin]字段参数都为一阶的RLC参数,所以放在一起说。

其实在hspice里对这种管脚对应好的RLC电路描述相信大家看到的比较多了,一般先用B-element来调用需要仿真的那个管脚对应的buffer,然后再用节点描述RLC电路

图18

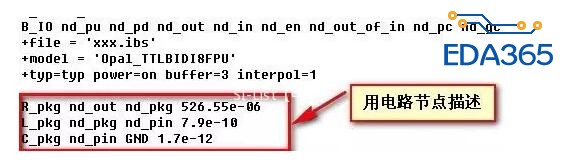

或者将RLC电路定义成一个子电路来调用

图19

但是我们遇到了[package model]怎么办,[package model]里不仅有管脚的自容自感信息,也有互容互感信息,要是还用上一种方法显然不太管用,要是能有一个方法,让软件在仿真中自动去取PIN脚的封装信息就好了,既可以不用自己去写语句描述,也不用担心粗心出错,一举两得啊,到底有没有这样的方法呢,答案是肯定的,有!

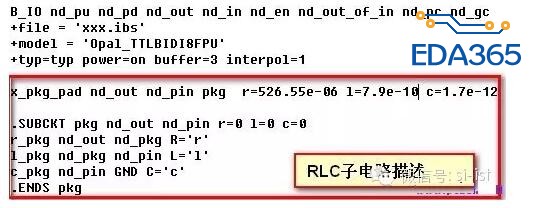

可能对hspice比较熟悉的童鞋已经猜到了,这个方法就是.IBIS Component Command,我们先看下这个语法的组成结构吧

图20

第一行的'ibis_name'指的是这个示例的名字,简单的说就是起个名字吧,没什么好说的。

第二行的file指的是指定一个.ibs文件,这个也没啥说的

第三行的component指的是.ibs文件中你要仿真的器件名称,因为.ibs文件里可能包含好几个器件,需要你手动选择下。

第四行的mod_sel和上面意思类似,因为一个管脚可能对应不同的buffer模型,你需要指定一个你想用的模型。

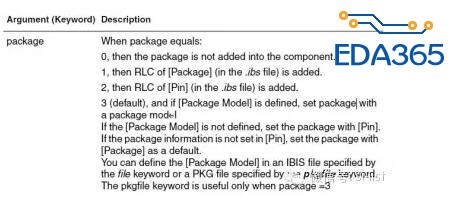

第五行的package我们需要着重说下,这个地方是重点,先来张截图

图21

截图是hspice的文档对这里package的说明,意思是这里的package有4个值可选,0指的是不调用任何package参数,1指的是用[package]字段里的RLC参数,2指的是用[pin]字段里的RLC参数。3的话是最有意思了,我们分个小段开看下

3的后面有个(default)字样,因为package这项是可选项,你要是不对它进行定义的话,那么package的值就为3,那3究竟是说明什么意思呢:上面说了,要是[Package Model]被定义了的话,那么3指的是用[Package Model]字段里的RLC参数,要是[Package Model]没有定义,那么3指的就是[pin]字段里的RLC参数。要是[pin]里也没有RLC参数的话,那么3指的就是[package]字段里的RLC参数。

这里我们也可以印证第一节得出来的结果,那就是这三个字段的调用优先级为[package model]>[pin]>[package]。

第六行的typ其实就是对应了.ibs里的typ max min三组数,不再多说。

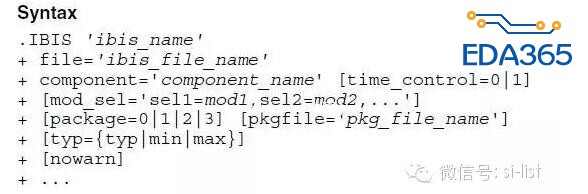

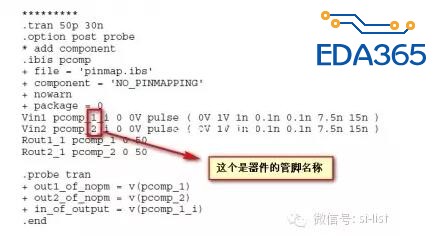

我们大致的把.IBIS Component Command的结构描述了一遍,看到这里有的童鞋可能会迷糊了,你这个.IBIS仅仅调用的是一个整的器件信息,没有涉及到单个管脚的内容,我到底怎么样才能对单个管脚进行操作,或者说软件是怎样把单个管脚和它对应的package参数联系起来的。这个大家先不要着急,咱们来看一个示例

图22

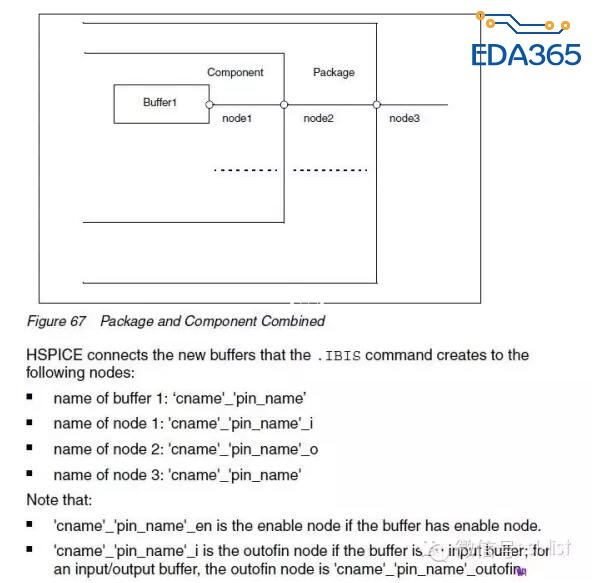

看了这个示例大家可能就有点明白了,我上面的红框圈起来的就是器件的实际管脚编号。其实只要我们知道了单个管脚buffer的节点就可以对单个管脚进行操作了,用.IBIS调用的buffer节点和B-element是几乎一样的,但是有点微小的差别,那就是节点是由ibisname_PIN_nd组成,假设我要对ibis_name为'pcomp'的第U1管脚的“使能”节点进行操作,那这个节点名称就为pcomp_U1_en,其他节点都类似,给大家截图节点说明图

图23

其实常用的节点是ibis_name_PIN_i,ibis_name_PIN_o,ibis_name_PIN_en,ibis_name_PIN(pin脚的最终输出或者输入),要是还有哪个童鞋仍然看不懂的话,就需要恶补下buffer节点知识了。

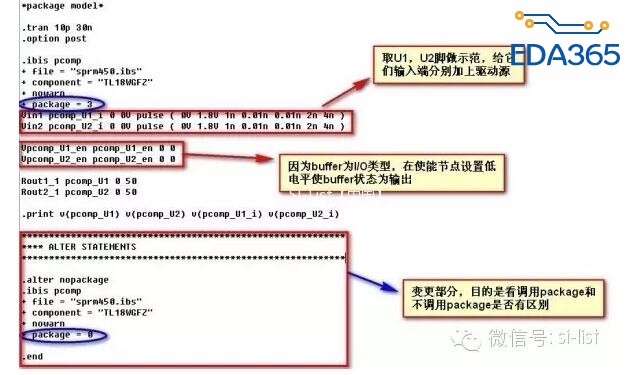

OK,理论的说完了,咱们应该亲自实践下看这个方法好不好使,实践出真知嘛,底下我们来进行一个示例来验证下这种方法是否能够正常调用[package model],由于带[package model]的.ibs模型不是很好找,附件会为大家奉献一个。

首先编写网表

图24

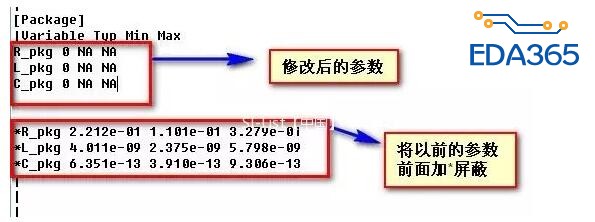

为了避免[package]的RLC参数对调用[package model]的RLC参数时有影响,我们把.ibs文件中[package]的RLC参数都改为0或者NA

图25

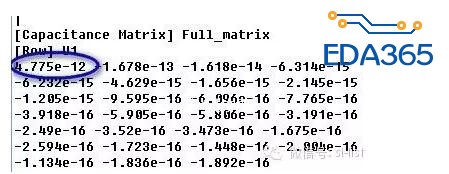

然后为了和网表中package=0时的结果对比更明显些,我们将电容矩阵中的U1管脚自容数据从4.755e-13改成4.755e-12

图26

OK,一切就绪,开始跑仿真。

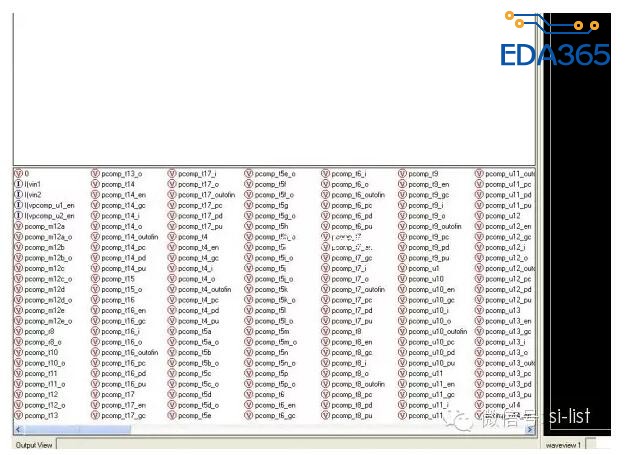

大家是不是仿真的时候很长,呵呵,确实是,跑出来的结果我们就可以看出来为什么要跑这么久

图27

图上可以看到软件把那些没有用到的管脚都跑了一遍,一共有105个脚,工作量当然大了,这里我没也发现啥好方法能有优化的,只能手动改.ibs文件了。所以电脑不太好的朋友就得注意了,很可能会跑卡住的。

接下来在对比下package=3和package=0的波形

图28

图上面是package=3也就是调用[package model]的RLC参数的波形,下图是不调用任何波形,能够明显看出来[package model]的RLC参数确实在仿真结果中起到了作用,说明我们的调用方法是可行的。

本文到此基本上就结束了,微信群内会附上示例网表和相关的.ibs文件供大家参考。

关于SI-list【中国】微信群

本群专注于:高速链路设计,信号完整性,电源完整性仿真,测试,验证相关技术交流,经验分享,解疑答惑,如方便,可把单位,研究方向在群名称表示出,方便大家交流合作,如果消息太多设置为免打扰模式,不便的可退群。

注明加SI-list【中国】微信群.

赞一个!

拜讀

CPU端的Vswing很小,使得CPU端的数据margin很小或者fail。每个channel接两根DR的UDIMM,DIMM端的drvier strengthen已经是最强(34ohm),有什么方法能使CPU端的Vswing变大,需要找DIMM厂家将DIMM的drvier strengthen再加更强的step吗?或者还有其他方法吗?CPU端的ODT已经调高

CPU端的Vswing很小,使得CPU端的数据margin很小或者fail。每个channel接两根DR的UDIMM,DIMM端的drvier strengthen已经是最强(34ohm),有什么方法能使CPU端的Vswing变大,需要找DIMM厂家将DIMM的drvier strengthen再加更强的step吗?或者还有其他方法吗?CPU端的ODT已经调高