DDR3_CLK差分对测量指标问题

最近在实际测试时发现对一些指标不了解,测试要求或规范也没说为什么要这么测试,这样就比较苦恼,就像design guide一样,虽然你按他写的设计就基本没问题了,但是你总想问个为什么。我真心希望以后这些规范指南能出个高阶版本,讲明个为什么,当然制定规范高手都是不屑说的,我明白。好了,牢骚发完,下面开始问问题,请接招。

差分对的测试中有几项不是很明白,就拿DDR3的差分CLK来讲:

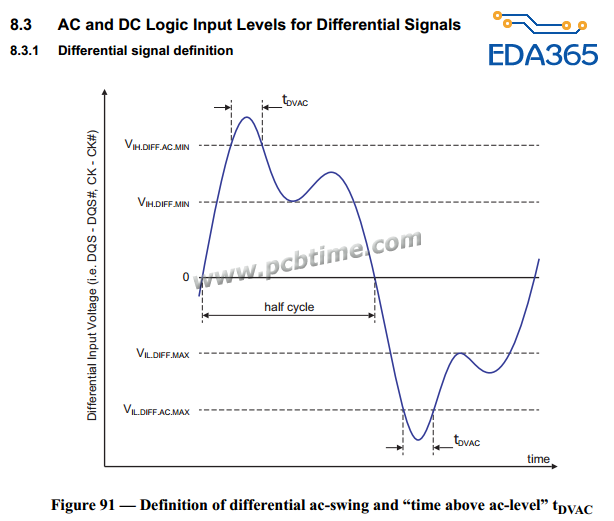

1、差分信号是在交叉点位置触发的么?但下图又怎么解释,还有个AC,DC电平?

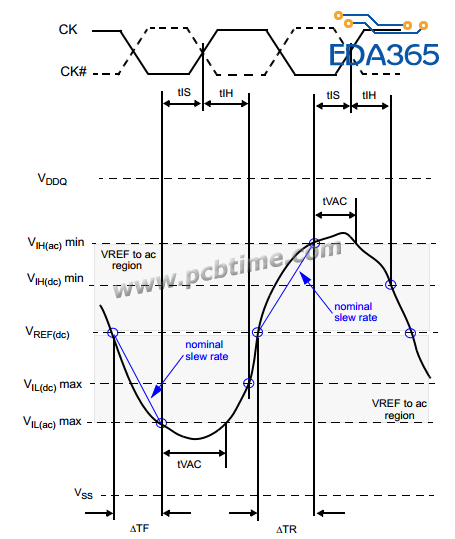

2、时序图里面又是从CLK的交叉点开始计算时序,从上图的电平触发角度来看又是差分的AC电平,那到底从哪个电平点开始计算时序?

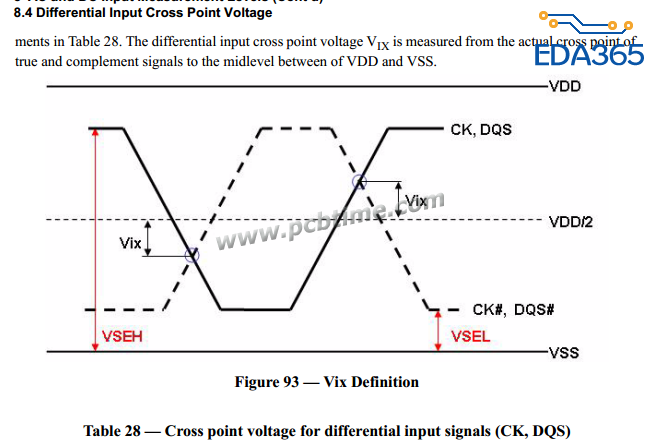

3、其单端信号有一个测试指标比较重要,即Crossover Voltage(交叉点电平位置),那么这个指标的重要意义为何?若出现问题可能与什么有关?

理想的读时序是从交叉点,但你要明白,没有这么完美的方波给你读,数字电路都是读电平的,不像模拟。

实际读时序,建立在AC threshold,保持在DC threshold。

还有Vih和Vil的持续时间是有要求的,达不到,那么源同步电路无法完成跳变和寄存器锁存。

这就是原因。cross point偏移会造成时序裕量减少。

我明白,考虑噪声的情况下数字电路必须有一个迟滞比较电路,所以有Vih,Vil

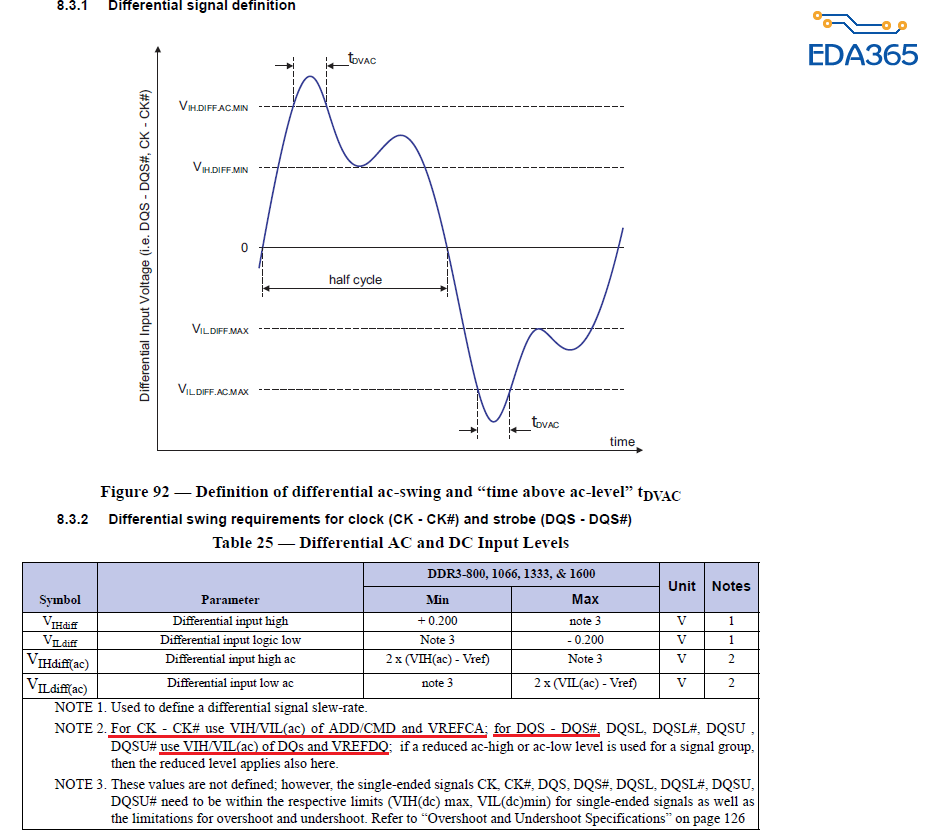

按道理差分时钟的触发电平应该不是交叉点,而是VIHdiff(ac),从其电平定义为2 x (VIH(ac) - Vref)可以看出,正好是单端的两倍。所以我才有这个疑惑,严格的来讲,应该从时钟的VIHdiff(ac)电平开始算时序。那么规范是为了简化计算还是给直接忽略掉这部分时间了,还是我哪想错了?

DDR3 Clock 是差分比較器,差分时钟的交叉点就是就是內部寄存器的時鐘沿,用來鎖存 Addr/Cmd 信號。所以時序以交叉點為基準點來定 Setup/ Hold time。

Addr/Cmd 信號是要被鎖存的單端信號,在信號轉態的時候,電平穿過 Vref 後至少要達到 AC 電平後才認可這個信號,這牽連到信號轉態後需要穩定的時間,所以使用 Setup time / tIS 規格。 當信號穩定後且被 Clock 觸取後,信號本身還要維持一段穩定的稱 Hold time,它的電平可以比轉態這種動態電平時略低一點,以 DC 稱呼此規格,它涉及 Hold time,時序規格就用 tIH 。

Crossover Voltage(交叉点电平位置),那么这个指标的重要意义为何?會出现问题 ?

VIX 的變化對應到時間軸就是產生 Clock Jitter,影響到時序的容餘。

那么怎么理解差分CLK的VIHdiff(ac)这个电平阈值的意义呢?

VIX 的變化對應到時間軸就是產生 Clock Jitter,影響到時序的容餘。

--能否详细讲解一下呢?让您费心了,非常感谢。

參考 JESD79-3E Spec.

就信號本身的要求而言,差分信號就如同單端信號需要通過一定的電平及維持一定的時間,

我們不希望差分信號只通過交叉點一點點就當成是轉態,這很可能只是 Glitch。

但就時序而言,它就是一個相對的關係,你會想那應該也要用 VIHDiff 點當基準點,這樣才

是的個認可的信號 (認可的基準點),但是因為這個點的時間是變動的,要定時序規格就會很麻煩,

用交叉點為基準,就非常明確,只要時序餘量把變動因素考慮進來。例如 Derating value。

另外,時序中有一個 CLK 與 DQS 的相對規格,你自己找找,也許它是以 CK/CK#的 X point 到

DQS/DQS# 的 VIHdiff(AC) 為量測點。

Vix 越大情況之一是差分信號的 V+ 與 V-信號的上升/下降沿的斜率差異越大,它可能造成

Duty cycle distortion,或 clock Jitter。但若保證它每一個周期都是完全一樣的歪斜,那每一個時脈

的周期還是可以維持一致。然而 Vix 若是太大,其電平對電路的實現可能也會有一些影響,所以訂

一個 VIX規格來限制差分信號正負輸出的 Slew rate 不要有太大的差異。

解释得很清楚,非常感谢,真的深究起来这里面东西还是很多的。

菜鸟学习了 谢谢