芯片管脚增加电感

时间:10-02

整理:3721RD

点击:

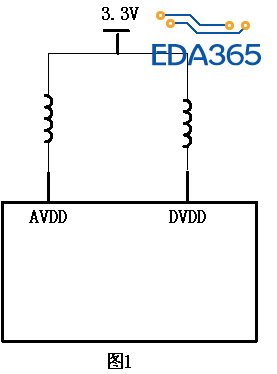

在实际设计过程中,许多PCB设计都会在把芯片的模拟供电脚(AVDD)和数字供电脚(DVDD)用电感或者磁珠来隔开,如图1.

根据前辈的说法,这是为了防止DVDD的电源噪声影响到AVDD上。这样看起来好像也没什么问题。

但是电源完整性设计就是要把PDN的阻抗做到尽量小,电源输入口加电感显然是不符合PI设计的。

那么问题来了,

1、电源管脚上增加电感和磁珠是否真的能隔离噪声?

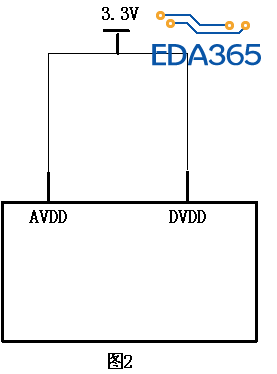

2、如果AVDD和DVDD不加电感而直接连到同一电源网路上,如图2。是不是说电源完整性做的越好,纹波越小,则DVDD在PDN上产生的噪声就会越小?

3、看到有的书上提到,EMI的根本原因是由于dI/dt造成的。如果是这样,那就算电源完整性做的再好,第2个问题也是否定的了?

请坛里的各位大神来帮小弟解答一下疑惑。

1.能,磁珠用于隔离电流噪声,特定频率消耗电流以热量形式转换掉。

2.那么你要保证AVDD的端口处PDN足够好,记住,是足够好。因为更容易受影响的是模拟电源。

3.理论上是如此,可是有些SSN不是光用电容能解决的,电流的噪声用磁珠的成本和效果要远远优于单纯的电容组合。

这个电感对于整个回路的电感来说是并联的,其对回路的影响不大,不影响PI设计。

放心的加吧,这是2码事。

:)

1.增加磁珠不就是相当于增加了阻抗么?PI设计不就是要尽量降低PDN的阻抗么?2.PDN的噪声是不是等同于纹波?

1.端口的回路阻抗以Z11为准,磁珠所接入的位置在Z21通路中,对Z11影响很小,这样你是否能理解?

2.Vripple=Z11*delta I 但是ripple小不代表delta I就一定小,delta I过小会影响DCDC的效率,这是一个均衡的过程,所以你要理解为PDN主要去耦合电压噪声,磁珠消耗电流噪声。

磁珠两端各加一个电容,可以保持阻抗恒定

磁珠前端也加电容可以恒定?

这是一个折中的选择,没必要纠结加磁珠与PDN阻抗,不是水与火的关系;选取合适的磁珠确实会起到隔离的效果,磁珠是带通滤波,关键看怎么用