关于上升沿变缓和下降沿变缓

时间:10-02

整理:3721RD

点击:

时钟上升沿变缓和下降沿变缓会导致时序混乱吗,如果是,除了时序,还会造成什么后果。

你是多少频率的咯,什么总线

40M的时钟,你就地址,数据,控制分别说下。

40M的时钟,你就地址,数据,控制分别说下。

时钟一般是点到点,40M也不高,一般没什么问题

时钟是这样的,交换机中用。数据量上了1g,不知道会不会有影响。

1

时序和寄存器判定高低电平的门限值有关,上升沿变缓以为这门限值在相位上延迟了,对时序当然有影响。

你给的时钟似乎只是个system clk,你要看速率和bus clk

你的上升沿是多少?如果是6ns的话,如果变缓一些的话应该问题不大,但是如果你的上升沿快的话,那么变缓的话可能会有影响,所以要具体分析。一般情况下,40MHz的时钟沿变缓一些应该不影响。

这些东西还在学习中,thank you

查了下datasheet,maximum4ns,按照你的说法来,应该是有问题的。从上面的小编的说法来看,光从这一点还不能确定,看来还得学习学习,才能搞懂。

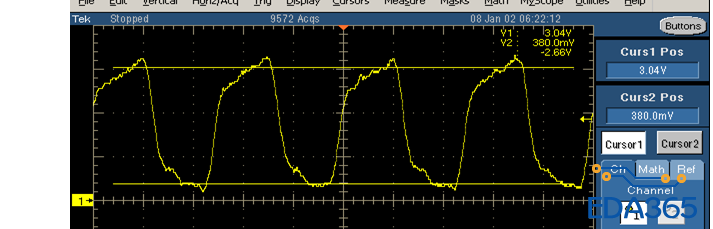

从图上看,阻抗没匹配好,应该是串接的电阻太大了

你这个问题比较严重,时序裕量太小了,需要看看你的clock的拓扑结构。如果是点对点的,那么你的驱动太小了,如果有串阻的话,可能要调整你的阻值。

照上面这样说,控制阻抗和选用板材。都会有一定的影响

从上图来看,应该不存在驱动的问题,因为时钟信号的幅值从300多mV到3V,信号的幅值很大,而且信号的速率很低,也没有明显的阻抗不匹配问题,至于上升沿和下降沿的变缓,还不存在太大问题。主要是看时钟信号跟数据信号之间的时序关系,如果满足建立和保持时间,是不会有太大问题的。对于这么低速的信号,我们还不用太多去考虑阻抗问题。

如果幅值不够,确实就会存在驱动的问题