捷波公司的电脑主板!(大家来找碴)!

http://www.eda365.com/thread-1183-1-1.html

2005年买了块捷波主板,买回来3天就点不亮了,换了个,接下的两年就是痛苦的煎熬,要么启动的时候见不到硬盘,或者莫名死机,忍无可忍2007年的时候,换了块华硕的,从此世界清静了。上月见到此强贴,苦心灌水1周,终获下载权限。

也闲着无聊,顺便开此帖学习下捷波主板layout,大家跟阿。我是一边看一边跟,所以大家有不同意见或者发现问题点要跟贴阿。

-------------------------------------------------------------------------------------------------------------------------------

花了3天,断断续续地看,写这个帖子。觉得表面上能看到的问题,基本在下面罗列出来了。这个设计工程师其实做得还可以,有些阻抗控制的叠层划分等都没出大问题。也没有一些常见的坏毛病。

大家也别认为我挑剔某些问题了,事实上我已经放松很多要求了,更细致的问题点,我都自我保留了。其他的布局篇之类的也就没精力看和写了。一方面没有原理图,另一方面自己能力还不够。

但不意味着这个帖子的讨论已经结束,从一个参考设计的大众评审,来评估大家心中的layout标准,对我们能力的提高很有帮助。因此不能听我一家之言了,大家踊跃回帖阿。

[ 本帖最后由 cmos 于 2008-3-28 14:30 编辑 ]

现在的主板几乎都是公版设计,忽略厂家偷工减料的因素外,在决定主板性能的因素里,layout占了很大比重。

LZ的做法非常值得大家学习,很多人都是为了搜集资料而下载文件,几乎很少有人去看过到底下载的是什么,很多新人刚注册就抱怨有些文件不能下载,其实就算能下载,全世界所有论坛都给你下载,资料多得把我们的硬盘都塞满了,又能怎么样呢?感觉很多人都有一个心理误区,就是好像自己下载的资料越多,心里就越充实,让人想起一些没文化的爆发户,家里书架却堆满了毛泽东选集和邓小平理论,却从来不会去看一眼。是时候静下心来好好学习了,我们论坛藏经阁里的书,任何一本能从头至尾学习完,都可能成为高手,不要让我们上网的过程成为搜集资料的过程,让我们都把宝贵的时间花在学习上,勤学好问,我想大家都能成为高手。

本帖将置顶一个月!

是的修铜工作量很大,但不是做不到,只是花时间而已。意味着你不能用auto shape来铺铜,而必须手动铺静态铜。

意味着,你需要额外的付出30~50%的layout时间,但是我要告诉你在我过去的10多年的layout生涯里,以及认识的众多做日单的同行里面,无锐角铺铜是layout工程师的基本要求,你有机会看日单的layout的铺铜,即便是数万Pin的设计,也是无锐角铺铜的,虽然有的时候要数名工程师额外的数周的努力。

所以不是不能完成的任务,只是你做了没有的。

其次就性能来讲,哪个性能更好,这个没有争议吧。

等我比较闲的时候贴一个sony的铺铜标准,你就知道啥叫标准设计了。

[ 本帖最后由 cmos 于 2008-4-14 13:41 编辑 ]

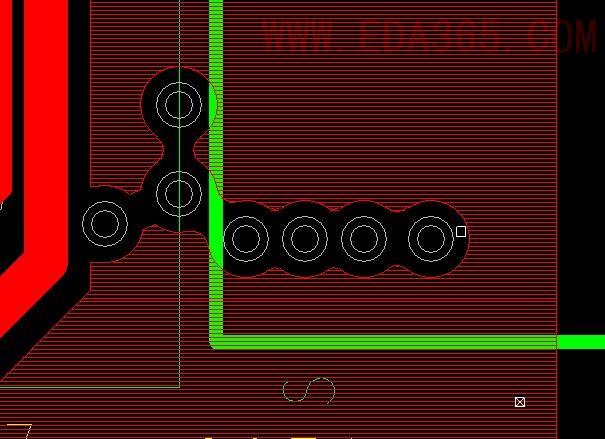

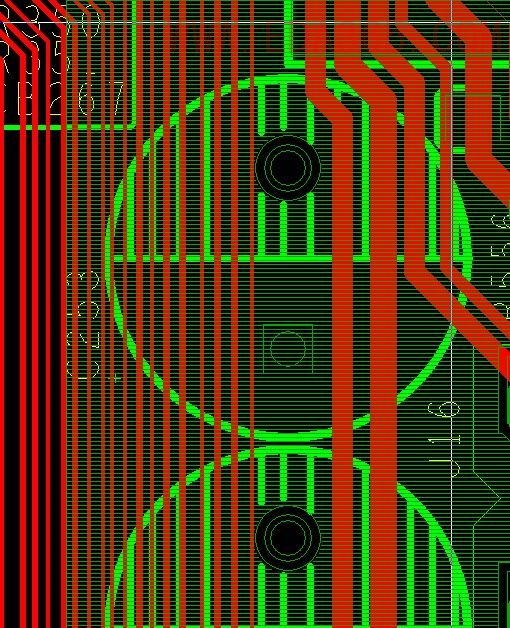

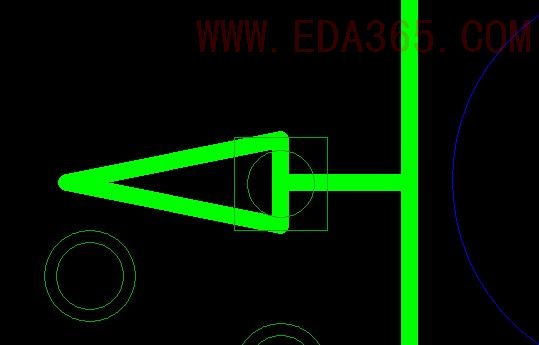

铺铜篇(以下case,择其一,均不累述)

1:大的铺铜,却在这里变成瓶颈,其实那个via打法是可以调整的

2:被via割断的浮铜

3:via删除了,铺铜没有调整就是这样的

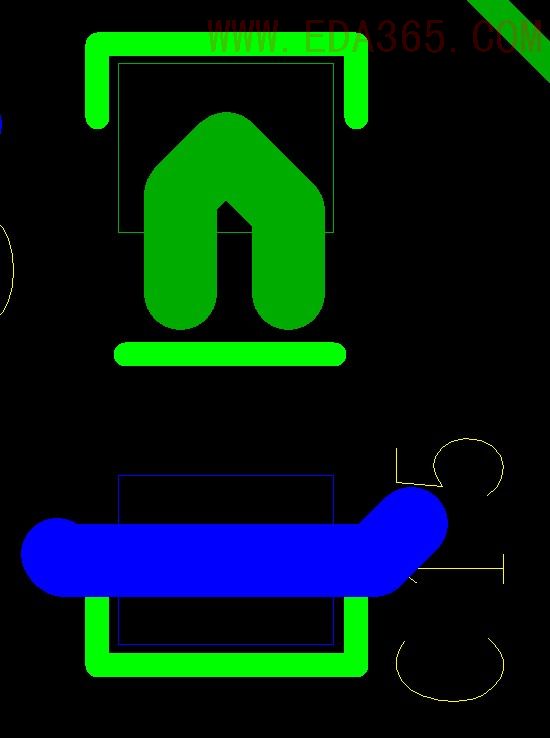

4:自动铺铜造就的小天线

5:从有利于焊接的角度,器件焊盘不要全覆盖更好。

6:其实从via看,上面多出的部分是多余的,多余的shape是否意味着,受影响的几率更大。

7:铺铜最好不要跨越焊盘进入器件内部,并避讳在此类小元件内打via.

[ 本帖最后由 cmos 于 2008-3-28 14:31 编辑 ]

需要加强对自己的规范意识,必须做的更好一点。

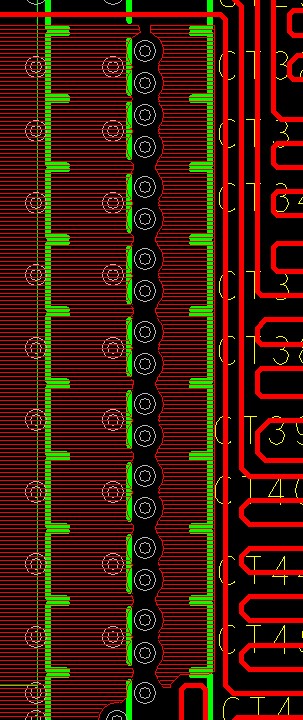

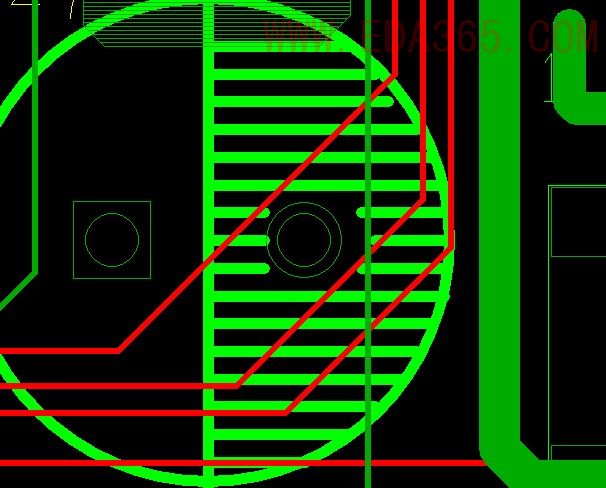

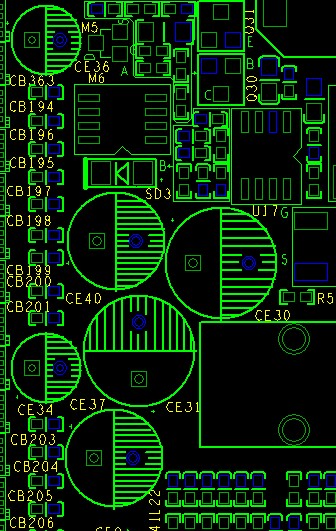

布线篇:

1:穿越0603,这个pci的rest信号,为啥有时电脑会莫名重启呢?先看看他们的rest是怎么layout的。

2:T分歧是无法避免的无奈选择,但也不是下图那样做的。

3:电源部的电容,被如此穿越。

此类电容一个比较热,另外电源和信号互相影响,即便有时影响可以在容忍范围内,在layout上却是可以做到最优化布线。

其实空间很大,为何要一定要从下面走,还要贴着管脚

4:BGA中出线,不在pin中间,其实constrain设好就ok了,道理就不说了。

5:可优化的差分布线,差分包地还可优化完整。

6:出焊盘锐角以及同级DRC,pair能做到对称出线最佳。

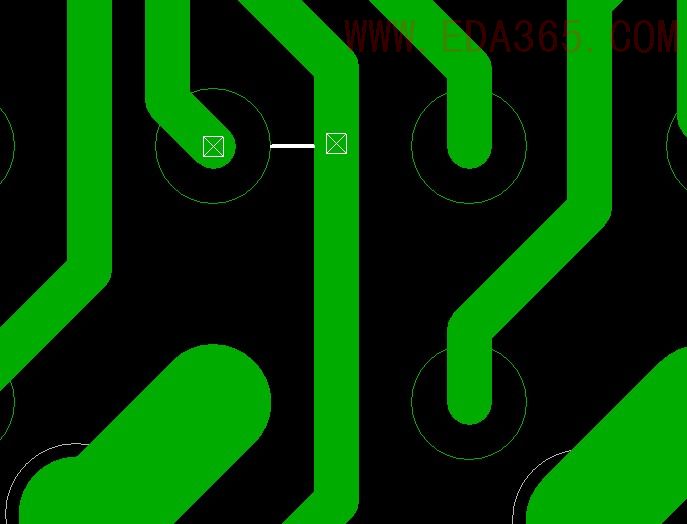

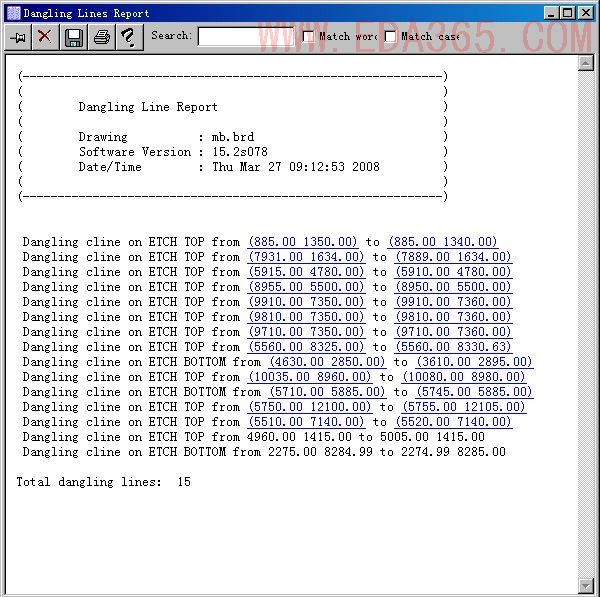

7:不知道为什么很多工程师没有check dangline的习惯,虽然有些躲在焊盘里的dangline不会造成影响,但是alllegro的这个功能还是能帮助我们找出真正的问题点。

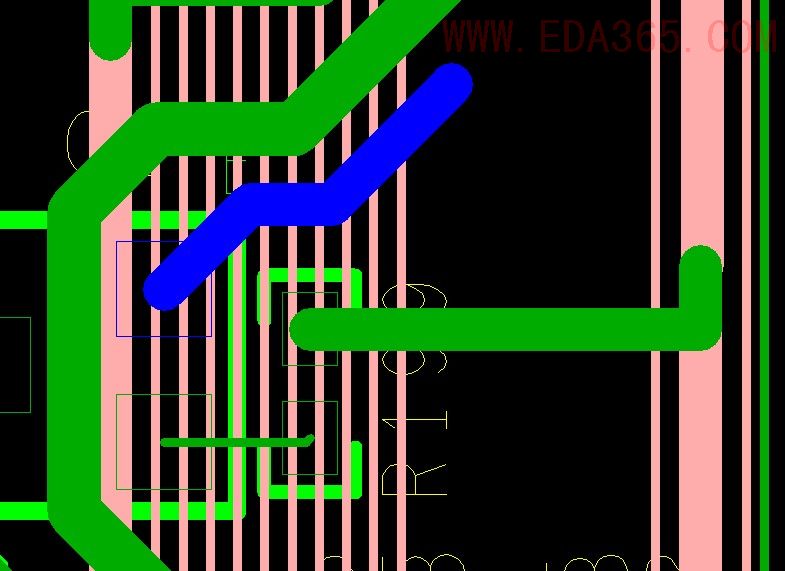

8:打的过远的地孔(蓝色线),可以就近打,bottom的bus绕开。当然还有电源信号穿越了那个三极管。

9:(前一项的bottom视图),gnd via 就近打孔,删除多余的conner,也是layout布线优化的一部分。

细节的处理体现出layoout的基本功,因为细节无处不在,体现出layout是否有良好的习惯。在高密度设计,这种坏习惯可能是致命的,会浪费很多宝贵的空间。

为什么出焊盘的via从来就没有能打正的。

10:cline与shape互连时要小心,不要制造锐角出来。

11:lock off的线,不是问题的问题,也是check中需要修正的一项。

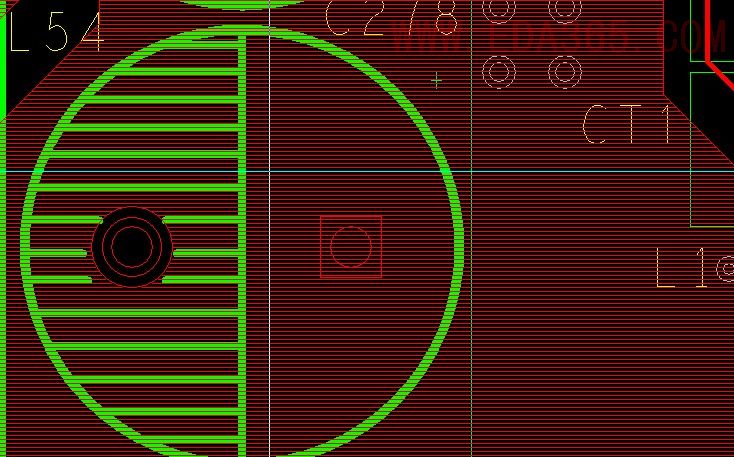

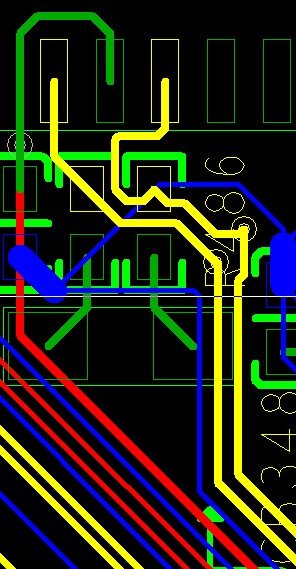

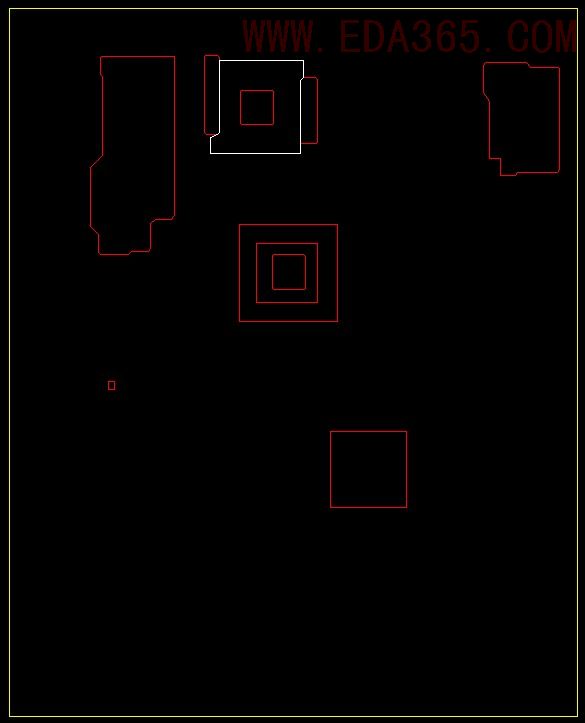

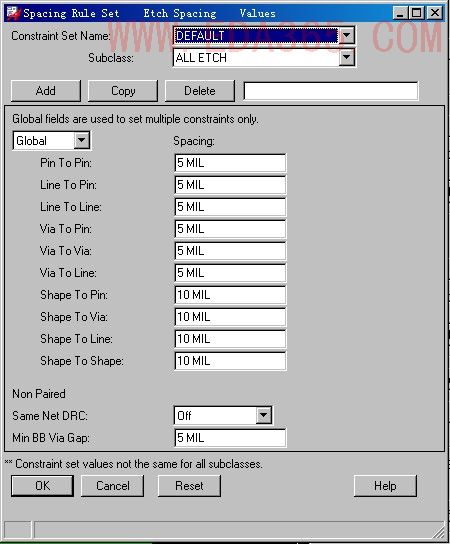

设置篇:

1:一个正确的constrain设置会帮助你迅速的定位到问题点,如果一个错误的设置意味着什么?

相关的constrain area,没有在相关的design rule找到设置,那么assignment table设了还有什么意义呢?

NET_PHYSICAL_TYPE = PWR

NET_SPACING_TYPE = BGA

2:layout可以选择给自己添麻烦,或者让自己随心所欲,但是往往牺牲的是性能,在空间容忍的范围内,尽可能的拉大间距,比如via&via,via&pin,power&signal等,可以给制造,焊接等多方面减轻负担,也是减少窜扰的一种方式。至少schematic来找你的时候,你可以理直气壮地说,我的layout做到最优化了。

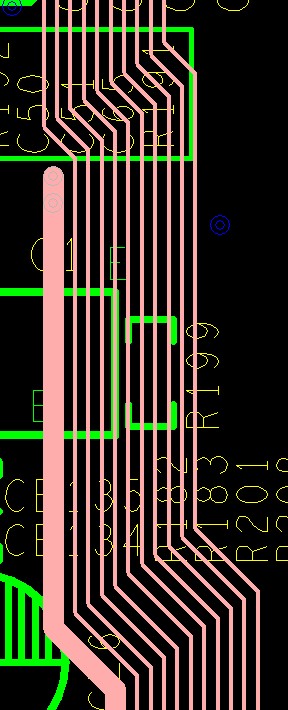

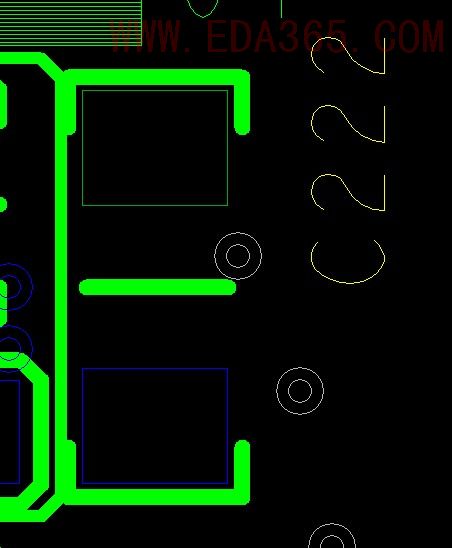

3:placebound top/bottom的作用,就是帮你在布局时指导你的间距,即便有的时候,你所认为的DRC是可容忍的,例如C94。

但不意味着其他的器件就有资格去穿越这个道德底线,造成的后果是layout无视此类drc,从而r268,r266的情况出现了。

4:4个方向放置的带极性电容

这个的解释可能比较牵强,就是在做贴装的时候,4个方向放就只能人工做,如果2个方向放就可以机器作了,但是有很多设计两方向放置的要求。我也不清楚真实原因。

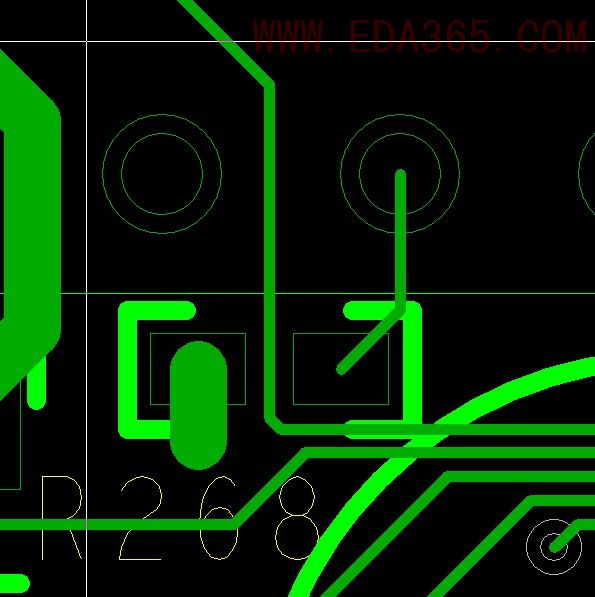

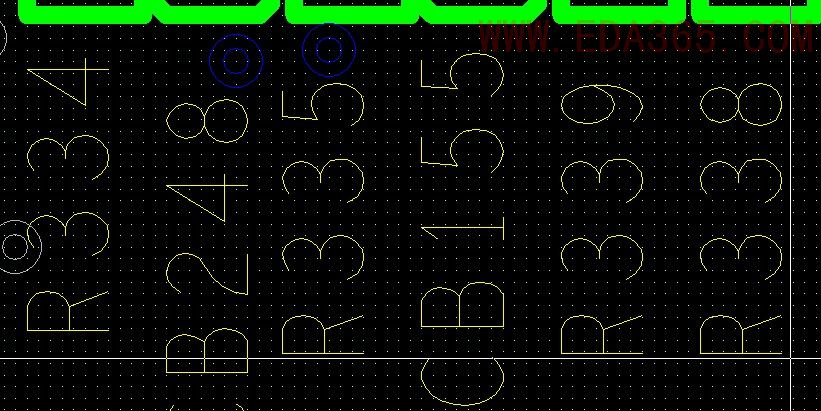

丝印篇:

这个是具有争议的内容,因为不影响性能,不同的公司有不同的要求,当然很多是没有要求。

我受过的教育,对于silk的具体做法是有具体的规定的,也许从silk的放置,可以看出这个工程师做事的细心程度,是否能做出完美的设计。

1:silk被设置成了0线宽,虽然在出gerber的时候,可以变成带线宽,但我不知道对做silk有什么帮助,(很遗憾,我现在公司的silk text也是0线宽)

2:silk 文本和器件丝印相叠

3:silk文本被via的drill打断。

4:叠在焊盘上的丝印

5:竖器件,横放丝印

6:没有摆正的silk名字(有空间的)

7:没有放齐的silk文本,如果用大格点放就能放齐的

8:silk文本相叠,需要考虑到最终的silk其实是有宽度的

9:尽可能减少辅助线,从而做到美观已经言简意赅的表达。

[ 本帖最后由 cmos 于 2008-3-28 14:09 编辑 ]

第四幅图还没有理解,不知道怎么就造成了小天线。是铜皮的尖角形成的小天线吗,怎样才能更好?是好修改一下铜的尖角吗? 请解释一下!谢谢!

[ 本帖最后由 changxk0375 于 2008-3-26 15:44 编辑 ]

值得学习呀!

铺铜原则上不能出现锐角,自动铺铜造成的小尖角,都是需要人工修整的,在高速信号中,都会感应噪声,代入地或电源。

虽然有的时候,这些都是在可容忍的范围,但也是针对不同的设计而言,从layout角度,做一个最优化的layout设计,并成为习惯才是主要的。

所以我常常会花大量的时间休整铺铜,虽然有人说对性能影响不大,只是个争议话题,你面对的客户不同,一个得过且过的客户,也就放过去了,如果遇到sony这类较真的客户,就会死的很难看了。

在主板的布线上,我很有兴趣,看了刚才贴出来的图,感觉在公司里的要求比这个要严格得多。有些东西我们这样处理的话是绝对挨骂的。

非常值得学习!

二当家的所讲极是,

鼓掌!

我想这只能说是捷波公司的LAYOUT头儿,抓的不紧了

好帖!

大有收益啊!

分析得有理有据,怎么看怎么像赶时间弄出来的。

布板的也太没有责任心了。