问个问题,8颗DDR3的芯片走什么拓扑比较合适?

时间:10-02

整理:3721RD

点击:

一个核心板,上面有8颗DDR3,咋样拓扑比较合适啊?

8颗同层走菊花链,还是双面各4颗走T型?

还是其他的呢?

8颗同层走菊花链,还是双面各4颗走T型?

还是其他的呢?

什么叫做读写平衡呢?

走菊花链

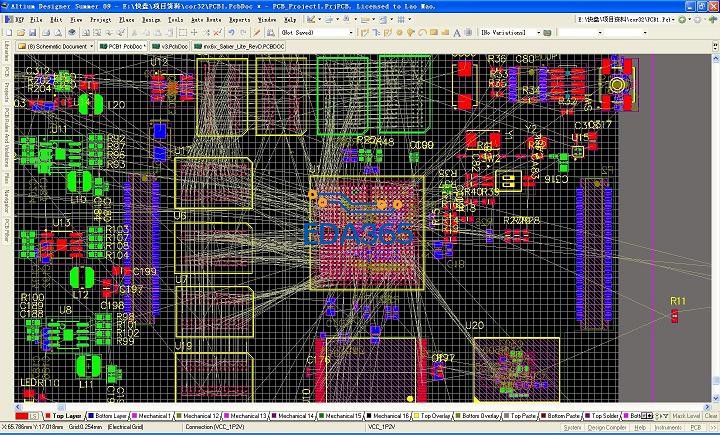

那帮忙看下这样的布局可以的吧?

可以的

做平板的吧,是64位系统,现在四核的平板都这个样的了。

不是平板,是帮一个朋友画的,图像处理方面的

试着把DDR3顶底对贴

目前我改成对放了,当时布局的时候没注意,这个线路是2rank的,所以只好对贴了,现在我在参考JEDEC Standard No. 21C,里面的布局

注意地址、控制驱动能力

推荐双面贴,因为按照你那样排下来地址线太长,可能拖不动。

我们的平板(原厂走线)时钟,控制,地址组走T型,数据组点对点,DDR3速度能跑到400多MHz。

小编,别人说走什么拓扑结构都没有用,关键是看您的芯片是支持什么拓扑结构的走线。通常DDR3是走fly-by结构的,但是也见过DDR3走T型结构的,而且走fly-by结构系统无法工作,究其原因是因为controller不支持读写平衡。所以还是要看controller是否支持读写平衡来决定。如果支持读写平衡就用fly-by结构,如果不支持读写平衡就用T型结构。

大家中文是这样说的,其实JECDE里面是说的“write leveling”。这是为了调节时序关系,通过CPU的寄存器来改变信号之间的时序关系,以达到设计的时序要求。需要更加详细的说明,请参看JEDEC的规范。

JECDE里面是说的“write leveling"是调整CLK与DQS信号之间的时序关系的.Memory Controller 会通过一些Training来调整CLK与DQS的时序关系。这种情况CLK与DQS信号之间是不需要做等长的。