请教关于内层差分的阻抗控制

时间:10-02

整理:3721RD

点击:

请教一下各位高手们:

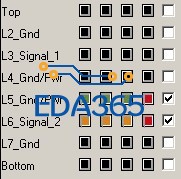

最近做了一块8层板,层叠是SGSPPSGS,第三层有几对差分线,设计时是参考第二层的GND的,第4层电源层差分线下方平面不完整。结果印制板厂反馈第4层平面不完整无法做阻抗控制。说内层差分线必须有两面屏蔽的参考平面才能做阻抗。

这个我不是太理解。按照自己的理解,参考平面是给差分线提供回流路径的,为什么一定要有两个参考平面才能做阻抗呢。而且SI9000里也是有差分线只有一个参考平面的计算模型嘛。

如果按照这样说,内层的单端走线是不是也要求必须有两个参考平面?

请各位高手帮忙解惑,非常感谢!

最近做了一块8层板,层叠是SGSPPSGS,第三层有几对差分线,设计时是参考第二层的GND的,第4层电源层差分线下方平面不完整。结果印制板厂反馈第4层平面不完整无法做阻抗控制。说内层差分线必须有两面屏蔽的参考平面才能做阻抗。

这个我不是太理解。按照自己的理解,参考平面是给差分线提供回流路径的,为什么一定要有两个参考平面才能做阻抗呢。而且SI9000里也是有差分线只有一个参考平面的计算模型嘛。

如果按照这样说,内层的单端走线是不是也要求必须有两个参考平面?

请各位高手帮忙解惑,非常感谢!

这个板厂应该说的有道理,同一根线如果不同段阻抗参考模型不同,则会影响很多参数,这个估计要分段计算和走线才行!

小编最后问题怎样解决的呢?

应该不会要求电源层是完整的平面. 我们也一直使用分割的电源平面的.

只要差分线没有换平面就可以了.

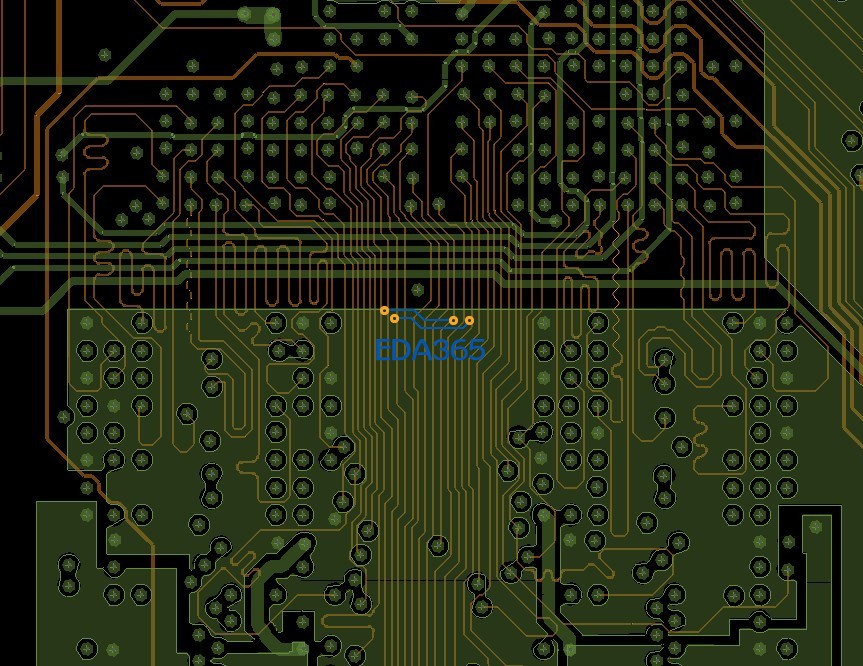

我这儿有一个八层板子,CPU与SDRAM的连接的地址走线区域对应的相邻层是不完整平面。

这是飞尔卡思的一个开发板。

八层板层叠

中间黄色的竖线大部分是地址线,它的下层是完整的地平面,上层是不完整的电源层。