DDR等长和LVDS等长的问题?(2440核心板设计同问!)

时间:10-02

整理:3721RD

点击:

各位大侠,小弟在布一个DDR2的板子,这个等长线让我很困扰!

CPU的总线到DDR2需要等长这个我知道,但是CPU的总线往往还到其他的芯片上,我这个等长是指CPU到DDR的最短距离,还是整个网络的长度啊?

我感觉是整个网络的长度!不知道有没有官方点的解释?

同样LVDS布线时也是这样两条线要求等长,其中一个要接电阻就长了一些,是不是另一个要走点蛇形线,把长度补回来,也就是整个网络等长?

怎么没人发表一下意见啊!

等长不是网络。是DDR到主芯片的走线长度。LVDS 的表述是对的!

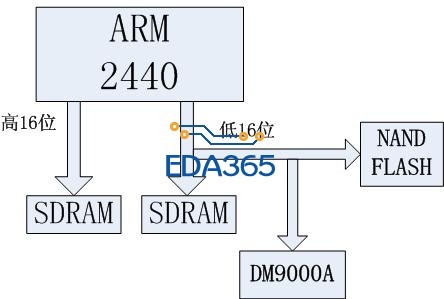

谢谢!还有一个问题,我的ARM2440出来的数据线上挂了很多器件,比如说SDRAM,FLASH还有DM9000这样需要总线连接的器件,SDRAM两片组成了32bit,而其他芯片都是16bit数据线的,那么ARM数据线的低16位的网络肯定很长,我觉得是不是保证ARM管脚到SDRAM的数据线长度基本一致即可,不是考虑网络,保证线的长短还是为了保证时序,而整个网络的长度我觉得是阻抗不同?还请大家懂得解释一下!

如上图:保证高地位数据线到SDRAM之前等长即可,过了SDRAM后不用考虑了吧?

同理的还有地址线!

假设2440高16位数据线到SDRAM有2000个mil,而低16位到FLASH和DM9000A或是FPGA可能会增加2000mil,这时数据线的高16位为2000mil,低十六位为4000mil,有必要将高十六位等长到4000mil吗?

没有大侠知道吗?

一直有疑问,大家讨论!

只要保证2440到SDRAM等长即可。

只要保证2440到SDRAM的等长就可以了吧,SDRAM和nand flash是没有等长关系的。