仿真SN74LVC16T245的问题疑惑

时间:10-02

整理:3721RD

点击:

仿真SN74LVC16T245的问题疑惑

使用SN74LVC16T245的IBIS文件进行简单的分析,想仿真vcca=1.8v,vccb=3.3v情况下的波形输入与输出

那么应该怎么才算正确呢?

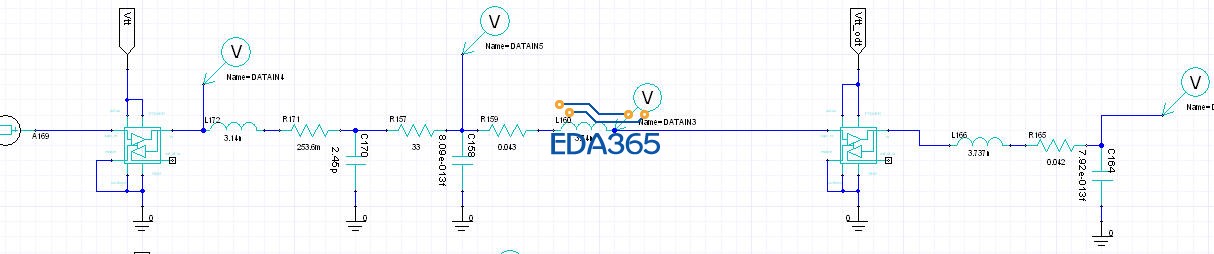

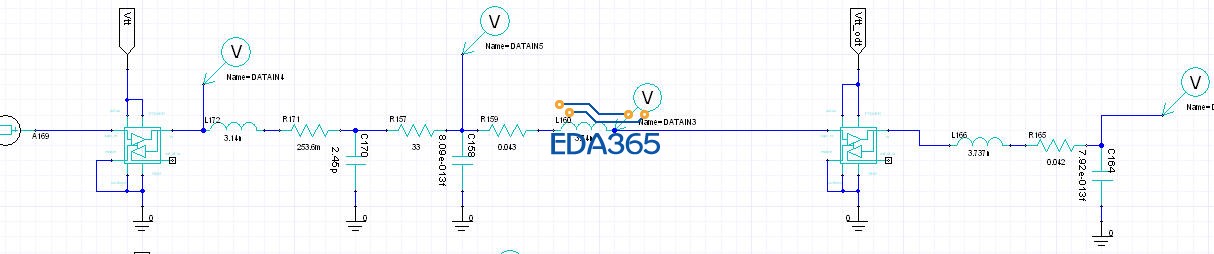

下面是我的电路结构:

使用fpga模型的一个SSTL18_II的IBIS,供电1.8v,输出端加上封装寄生参数RLC

中间加一个33欧电阻

然后直接连接到LVC16T245_IO_33,输入输出加上封装寄生参数RLC

怎么看输出波形比输入波形更缓呢?

使用SN74LVC16T245的IBIS文件进行简单的分析,想仿真vcca=1.8v,vccb=3.3v情况下的波形输入与输出

那么应该怎么才算正确呢?

下面是我的电路结构:

使用fpga模型的一个SSTL18_II的IBIS,供电1.8v,输出端加上封装寄生参数RLC

中间加一个33欧电阻

然后直接连接到LVC16T245_IO_33,输入输出加上封装寄生参数RLC

怎么看输出波形比输入波形更缓呢?

应该是看上升时间和下降时间吧