双面板问题

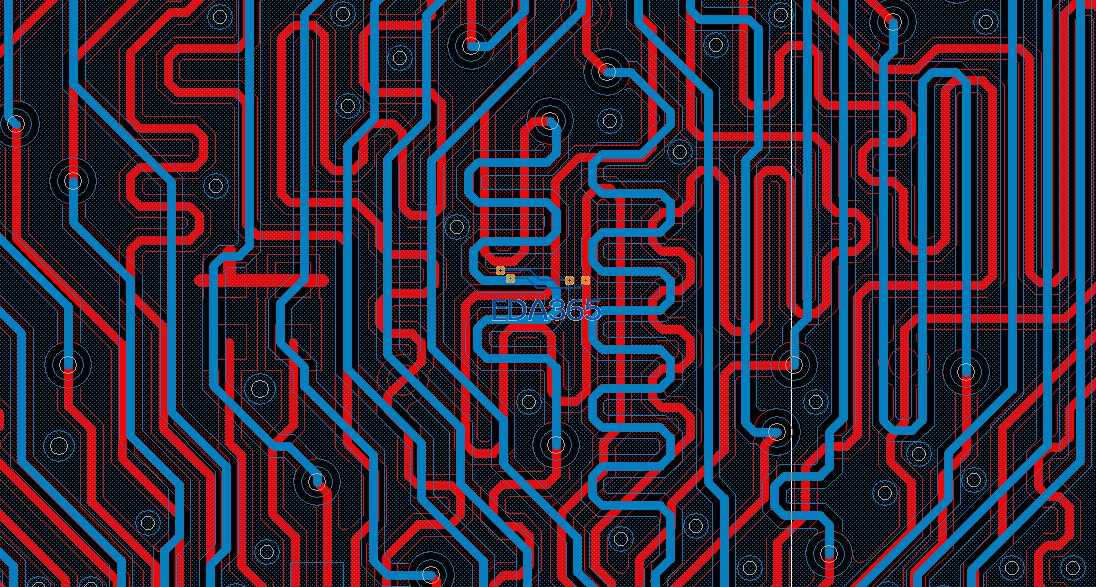

166M的时钟周期6NS,长度1300MIL不会引起时序问题,不用等长。但是两层板都有走线会引起很多信号完整性问题。

那就是下面一种方式比较好吧。

不用绕等长是要看“数据最长和最短之差、地址最长和最短之差、还有地址最长和数最短之差”与速率来决定的。

1300 mils对于6ns来说是“短线”,其实也不用太过分考虑回流了。

2楼、4楼说的有道理!

把底层当参考地!相差400mil不是问题。

不必做等长的,1英寸才140ps左右的延时呀。比如CLK=200MHz,周期5ns,半周期2500ps,它的1/20=125PS,相当于700mil的走线延时啦。所以不用等长的。我连clk=400MHz的都不走等长,跑的很稳定。即DDR2-800MHz。

你这是双面板啊?顶底层都走线了,信号没有参考地阻抗是无法控制的哦。除非你不控制阻抗。

此图两层板?没有参考层做不到阻抗控制,串阻也就变成阻抗突变的地方了,要了反尔影响信号。

是撒,只能靠伴地处理了,倒是想一层走线,另一层能铺地,BGA形式的貌似一层搞不定唉,不知道有没有人双面板DDR的走线经验分享下哈。

ddr走两层,没参考层?太不安全了吧?

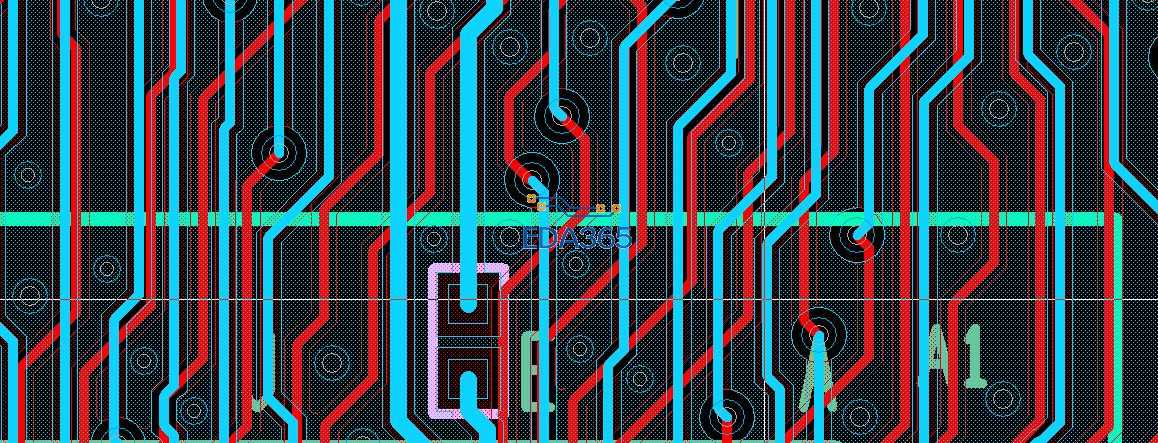

我就是走的BGA啊,2层DDR2-800,不走等长线,跑的很稳定啥。数据线不打孔保证在top层走线,底层做参考层,所有数据线不要超过1inch,如果有串阻请靠近DDR侧这样的数据线不要超过1.5inch,地址控制单向电阻放在控制器侧。时钟做100-120的差分阻抗,在ddr侧做差分端接阻值200欧姆左右,时钟差分串接电阻可调33-100R之间。驱动如果1对1请采用半驱。

高手啊,可否发一个图片看看,学习下哈。还有地址线如何处理,如果是1000MIl的话估计两芯片距离挺近的吧。

地址线可以打孔线长可到2.5inch,串阻。因为地址的频率只有时钟的一半。