内层阻抗计算H高度问题

时间:10-02

整理:3721RD

点击:

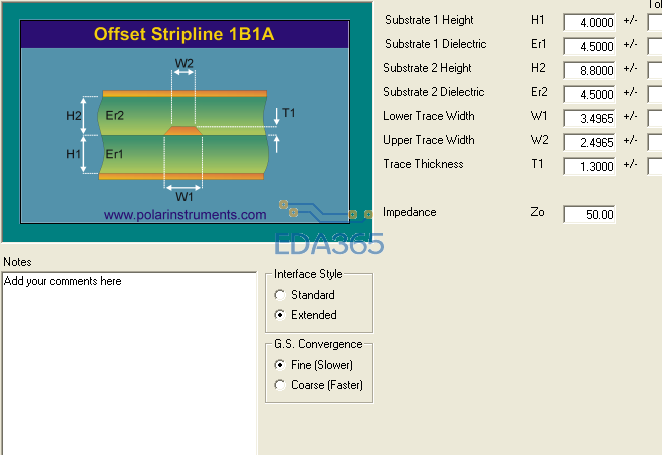

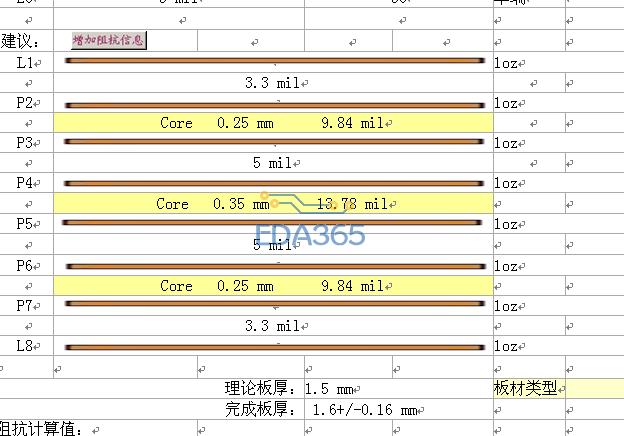

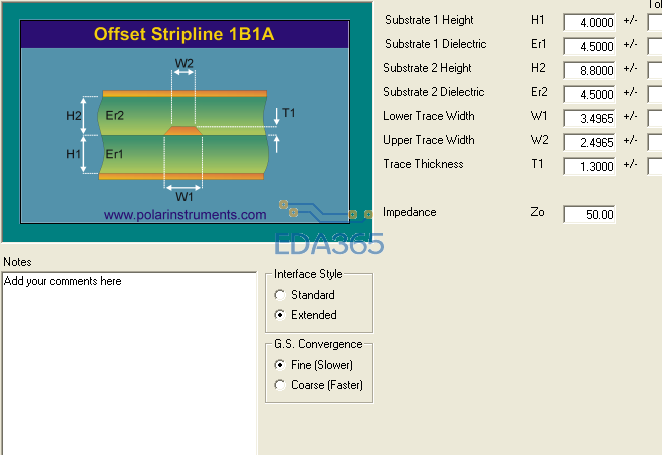

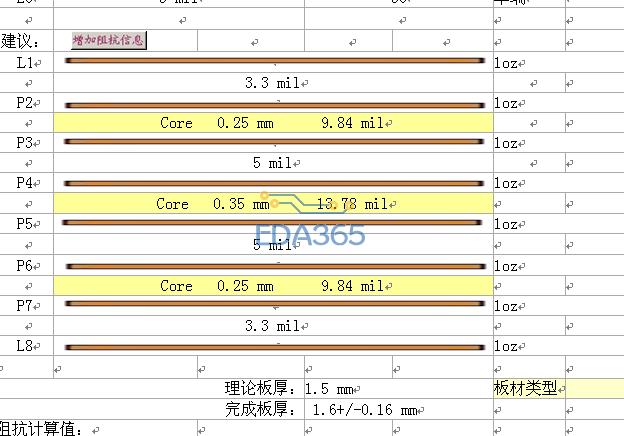

板子叠层如下,其中:L1,L8,P3,P6为走线层,其余为电源/地层。在用Polar SI9000计算内层阻抗时,如下图所示的H2高度为多少呢,是5mil(即PP厚度)呢还是5+1.4=6.4mil(即PP+铜厚)呢?求教...

建议5

PP+铜厚,因为线是嵌在PP里的。

按照5计算的话就是说H2为5,那板子在计算厚度的时候就会忽略内层铜箔厚度。这显然是不正确的啊。你说的5是指的H2高度吗?还是按照5计算比较好呢?

那实际板厂在做的时候,上的PP厚度不是5,而是比5大一点的数,以保证压合后的PP厚度为:有铜的上方为5,无铜的上方为5+铜箔厚。是这样吗还是其他?,

小编这种情况可以用另外一个计算模型来算!

什么模型呢?

按小编的叠层厚度,

H1应该是是9.84,

H2应该是是 5-铜箔厚度

叠构表明 P7层和P6层是有铜Core,再根据蚀该的方向,那说明H1是 9.84 mil

P5层与P6层之间的PP是 5 mil,但PCB压合后,在有铜的地方,PP的厚度应该 原PP厚-铜厚。

另外,感觉如果是1,3,6,8 走线的话,干嘛要用9.84 mil的Core?,让第1层与第3层,同时参考第2层不好么?,为什么要让第3层去参考第4层?

压合以后PP的厚度会薄。这和残铜率有关系。

评估叠层计算阻抗的时候,PP的厚度按照理想的来算。板厂会帮你调整。