关于DDR2数据线走线

时间:10-02

整理:3721RD

点击:

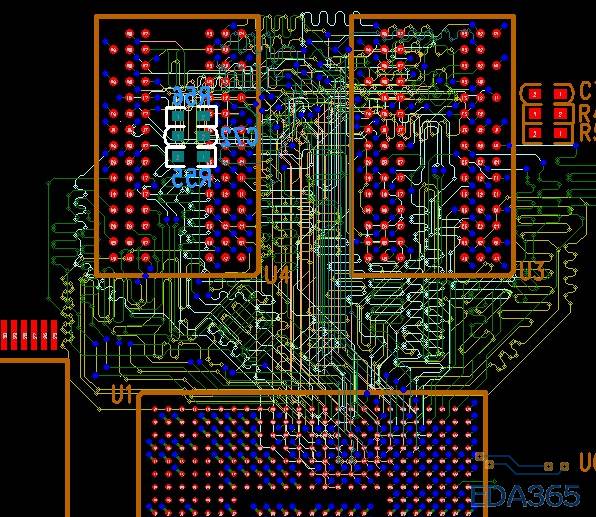

第一次画DDR2的ARM板子,查了些相关资料,有人说数据线需要需要同组同层,可是我现在ARM片子的BGA封装导致难以做到,现在的想法是同组走在同两层,以避免过孔带来的走线长度差,但是难以避免回流的断开,我想两层同时控制阻抗50,想请问下高手,我这样可以不?

这个布线要安排在完全以中间层对称的层上

LS能详细说一下吗?

小编最好截图!就算是BGA DDII 为了保证电气性能,数据线最好不要换层走!机构容许的话,不是特别小的板子,这点是完全可以做到的!

我的BGA间距只有0.65,现在走了4mil线宽,4mil间距,第三层焊盘就没有办法扇出了啊

上传截图

0.65BGA内走线用neck模式可以扇出不。如果成本不限制,可以考虑用盲埋孔。

为啥不用0.8mm

楼上的,小编说的是芯片就是0.65间距的,如果完全扇出,可以考虑0.3-0.15的VIA,4mil出线,或者0.4-0.2的VIA,出3mil的线。但可惜一般的PCb工厂都加工不了

不用同组同层的,随便放在哪一层都可以(除地平面外)

0.65的 pitch不错了,你试试0.5的通孔看看

感觉这个BGA最外面的2排不用扇出吧? 信号直接走表层,3-4排再扇出。这样可以用比较普通的工艺来做板。

一般人家设计BGA芯片的时候就考虑过这个问题了的,1-2直接表层,3-4扇出,走下面的一层这样。

数据最好走同层,如果走不下走不同层也可以的!

前辈请家教一下,孔径增大了,为什么线变细了,选3mil呢?

DDR2说是同组同层,其实不走同组同层也是可以的。线长把过孔考虑进去就可以。

DDR3的话不知道,没有实际布过。