关于前仿真时叠层设计的具体思路

时间:10-02

整理:3721RD

点击:

最近一直研究这个叠层设计,不过看到的大部分参考资料都是关于已确定的叠层参考设计,还有就是阻抗的如何计算之类的。但是具体的操作思路都没有看到。今天请教了个师哥,有所了解,贴出来让大家分享指正下哈:

1.首先根据板子里的BGA的扇出来评估需走几层板,并分配好各层板的属性;

2.根据pin脚间距来确定钻孔大小(似乎有几个常用值)和走线大概宽度及走线所处叠层(一般走线宽度4、5、6mil,更低可走3mil),注意钻孔的安全间隔距离;

3.将叠层设计与走线宽度,各层大概阻抗等要求与PCB厂商协商,厂商将反馈一个包括改进参数,和叠层厚度等具体信息的方案,可以互相协商;

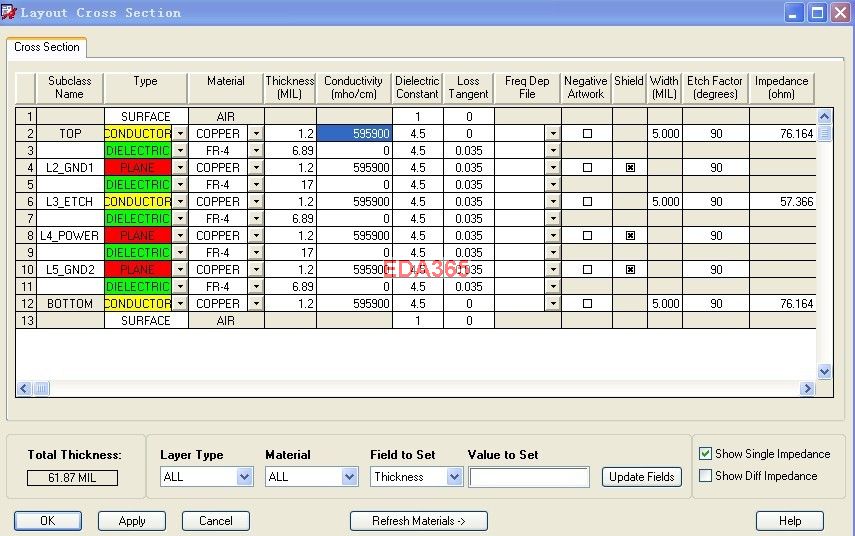

4,根据厂商提供的数据利用SI软件可完成叠层的阻抗确定。完成叠层设计。

我是新手,还没具体操作过,所以如果有不对或者不完善的地方请大家指正啊。

最近一直研究这个叠层设计,不过看到的大部分参考资料都是关于已确定的叠层参考设计,还有就是阻抗的如何计算之类的。但是具体的操作思路都没有看到。今天请教了个师哥,有所了解,贴出来让大家分享指正下哈:

1.首先根据板子里的BGA的扇出来评估需走几层板,并分配好各层板的属性;

2.根据pin脚间距来确定钻孔大小(似乎有几个常用值)和走线大概宽度及走线所处叠层(一般走线宽度4、5、6mil,更低可走3mil),注意钻孔的安全间隔距离;

3.将叠层设计与走线宽度,各层大概阻抗等要求与PCB厂商协商,厂商将反馈一个包括改进参数,和叠层厚度等具体信息的方案,可以互相协商;

4,根据厂商提供的数据利用SI软件可完成叠层的阻抗确定。完成叠层设计。

我是新手,还没具体操作过,所以如果有不对或者不完善的地方请大家指正啊。

1.首先根据板子里的BGA的扇出来评估需走几层板,并分配好各层板的属性;

2.根据pin脚间距来确定钻孔大小(似乎有几个常用值)和走线大概宽度及走线所处叠层(一般走线宽度4、5、6mil,更低可走3mil),注意钻孔的安全间隔距离;

3.将叠层设计与走线宽度,各层大概阻抗等要求与PCB厂商协商,厂商将反馈一个包括改进参数,和叠层厚度等具体信息的方案,可以互相协商;

4,根据厂商提供的数据利用SI软件可完成叠层的阻抗确定。完成叠层设计。

我是新手,还没具体操作过,所以如果有不对或者不完善的地方请大家指正啊。

最近一直研究这个叠层设计,不过看到的大部分参考资料都是关于已确定的叠层参考设计,还有就是阻抗的如何计算之类的。但是具体的操作思路都没有看到。今天请教了个师哥,有所了解,贴出来让大家分享指正下哈:

1.首先根据板子里的BGA的扇出来评估需走几层板,并分配好各层板的属性;

2.根据pin脚间距来确定钻孔大小(似乎有几个常用值)和走线大概宽度及走线所处叠层(一般走线宽度4、5、6mil,更低可走3mil),注意钻孔的安全间隔距离;

3.将叠层设计与走线宽度,各层大概阻抗等要求与PCB厂商协商,厂商将反馈一个包括改进参数,和叠层厚度等具体信息的方案,可以互相协商;

4,根据厂商提供的数据利用SI软件可完成叠层的阻抗确定。完成叠层设计。

我是新手,还没具体操作过,所以如果有不对或者不完善的地方请大家指正啊。

路过。