关于总线多负载的走线请教

时间:10-02

整理:3721RD

点击:

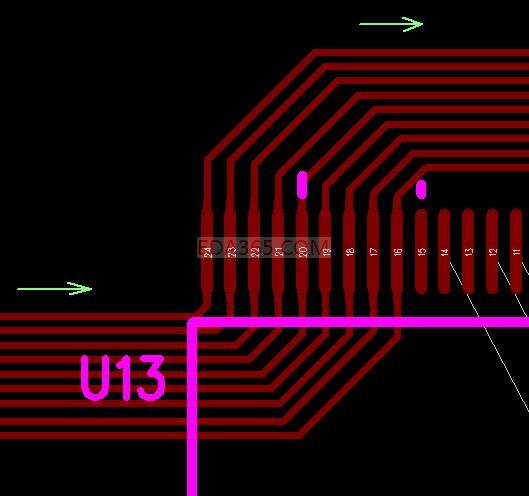

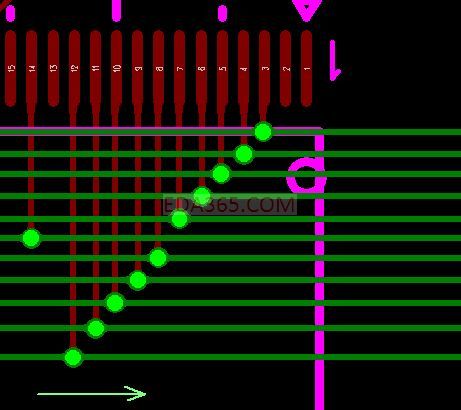

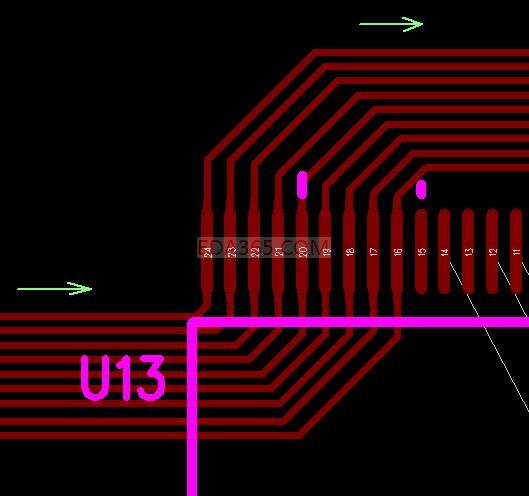

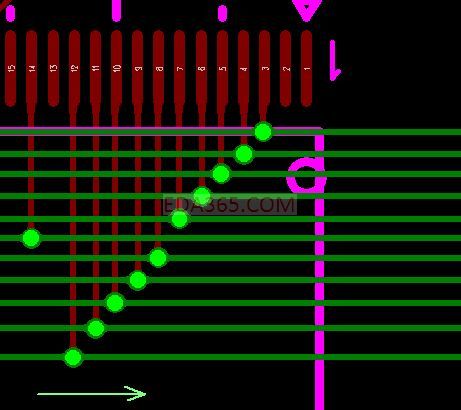

在总线有多个负载时,走线与负载的联连方式如下:

图一的走线对阻抗的连续性较好,但布线难度大。

图二的走线布线相对简单,但是存在过孔及stub 太长的问题,必定影响阻抗的连续性,并带来反射。

各位讨论一下,这两种走线方式哪种常用?

图一的走线对阻抗的连续性较好,但布线难度大。

图二的走线布线相对简单,但是存在过孔及stub 太长的问题,必定影响阻抗的连续性,并带来反射。

各位讨论一下,这两种走线方式哪种常用?

这种多负载的连接,一般速率都比较低,过孔及stub影响可以忽略了。

主要是通过仿真看看信号质量就可以了,如果是菊花链结构,前面几片波形可能有回沟。

图一的走法,将U13对后续接受端的影响减到最小,但后续接收端对U13的影响依然很大(如果后续接收端没有终端匹配时)。需要仿真确保Stub不影响信号质量,或确保Stub远小于工作频率的波长及跳变沿电长度。

设计PCB时,如果数量太多的过孔在一起,最好是4个一组,这么打一排下去,看的头疼。

有回沟的话,如何解决?

小编,四个一组是什么意思? 一排打下去是把GND 搞成一个槽沟出来是吗?

后续接收端对U13 的影响是什么方式的影响,反射?

“如果后续接收端没有终端匹配” 是指用什么方式的匹配? 如果是总线上挂了多个负载,每个后续负载都要匹配吗?

是的,设计PCB时,可以允许地平面有孔,但不允许有长的沟槽。

4个一组是因为很多总线是8位,16位,32位,64位等等。他们都是4的倍数。

4个一组分开打孔,不要打成一条线,打断了铜皮。

一般情况下下冲与过冲是同时出现的

不知道你这里说的回沟是属于下冲还是非单调

学习了!~赶紧修改去

非单调的,怎么处理?

看过了