SDRAM时序计算

时间:10-02

整理:3721RD

点击:

关于sdram时序计算:

cpu:S3C2410 SDRAM : HY57V561620

from:cpu to sdram

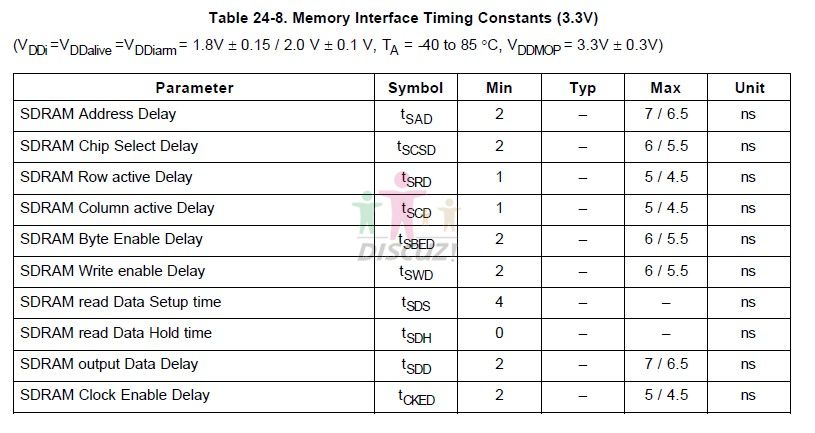

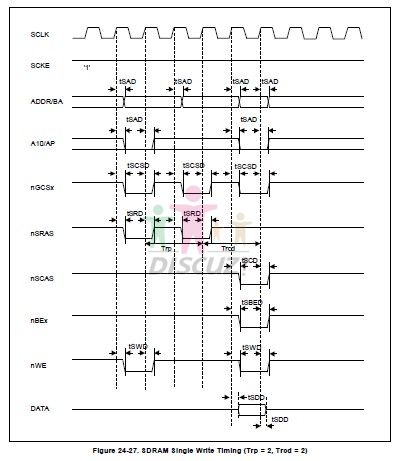

cpu的参数和时序图如下:

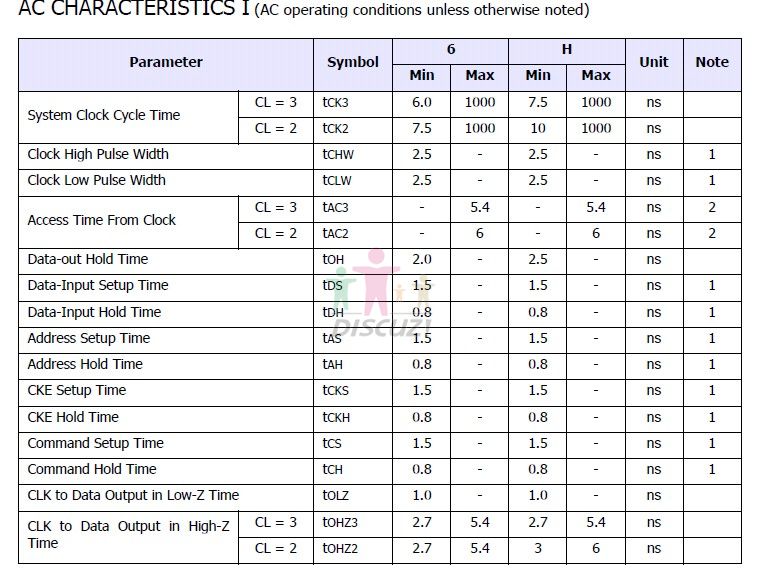

SDRAM参数:

以cpu写数据为例:

数据线飞行时间计算公式: Tft_max<Tclock -Tcomax_driver - Tskew - Tjitter - Tcrosstalk - Treciver_setup + Tft_clk

按sdram数据表,以cl=3,则Tclock=7.5 Treciver_setup=1.5

按cpu数据表,Tcomax_driver=Tsdd=7

忽略其他项,则Tft_max - Tft_clk<7.5-7-1.5=-1

由此推出时钟线比数据线长6in

不知道是不是计算有问题,

上网查了下,有些数据手册要求sdram布线时,时钟线要长于数据线

根据经验,这个数值太大了。再仔细算算。

我也感觉结果有些不对劲,但我找不出那个地方有问题,还请大家指点迷津啊

我不是做si的,但我知道一个通用的规则:clk大于其它有线.1.5inch<data<6inch.其它无所谓。

三星垃圾,好不容易弄到模型,测试负载和Vmeasure等数据又没有,翻遍了数据手册也没找到,无法仿真,xx棒子

模型里面连这个都没有,那还叫模型吗?

LZ,三星的模型你是怎么弄到的?

给三星发了邮件,三星不鸟我,又翻了遍数据手册还是没有,无奈,参考2440的模型设置了相关参数 ,

实际上时钟是100M,因此要按10ns算,仿真出来时钟flighttime是-0.7ns,最终算出的结果是Tft_max_data<0.6ns,Tft_min_data>-1.1ns,