层间切换走线阻抗的理论计算

note:众所周知,一些SI工具(Hyperlynx,SQ...)会对层间切换走线给出一个阻抗值,但我们看不到这些工具的源码,我们并不清楚这些EDA巨头是以何种方式来进行理论计算的。想清楚的是这个实际的理论计算过程,而不是通过工具得到的最终结果。

“需要理论计算过程”

请高手指教

[ 本帖最后由 forevercgh 于 2008-1-21 08:42 编辑 ]

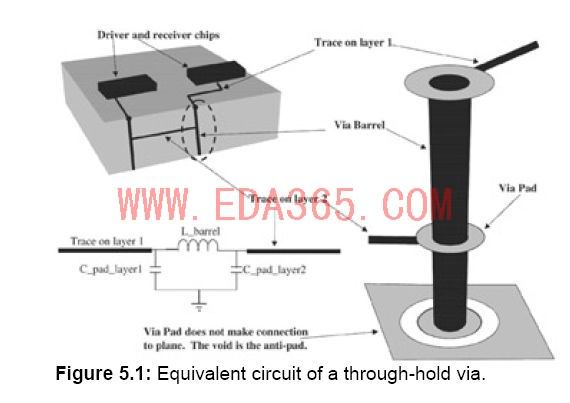

层间切换除了保证切换的两个信号层阻抗一致外,还要使过孔阻抗也一致,对于比较高速的系统,过孔都要建模,比如HFSS通过建立过孔的焊盘大小,孔径,孔的长度等参数,提取出S参数,再转化为spice模型,而其它一些2D或2.5D的仿真器可提取出RLC参数用于仿真,如specctre,但是精度没有HFSS的精度高,要想了解具体的计算过程请查看相关文档.

虽然不是很清楚地知道细节,但是可以猜一下:

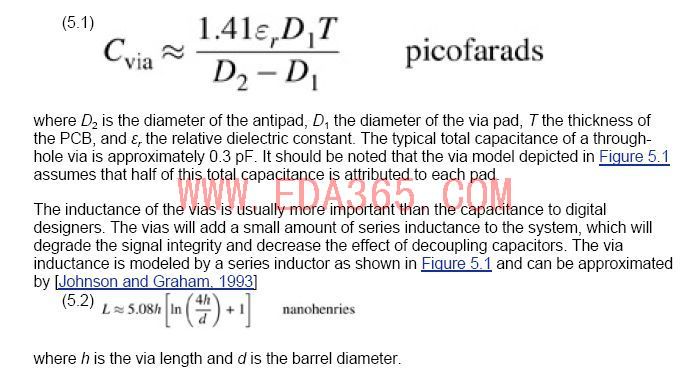

实际上你的问题就是问过孔对阻抗的影响,阻抗的计算公式里,只跟L和C有关系,这个肯定要先建个过孔的模型出来,只要能把过孔的寄生参数提取出来问题就差不多解决了。

寄生电容和寄生电感的计算:

这样是不是很简单就搞定了?不要问我计算细节,我对这个没兴趣。

至于埋盲孔,只要把相应的焊盘和STUB去掉就行了。

多谢两位大师点拨。

相关资料会进一步查阅

allen的图及公式应该出自 High-Speed Digital Sysem Design

[ 本帖最后由 forevercgh 于 2008-1-23 08:27 编辑 ]

谢谢

整个层间切换走线的阻抗理论计算?

不明白你这里说的阻抗是什么阻抗。层间切换走线整体来说,没有特性阻抗,因为各处的阻抗是不一致的。直流电阻没什么实际意义。

为什么要算整体的?分开处理能很好的分析对信号的影响。

迷惑中。

阻抗跟工艺关系很大。举个例子,有一家PCB厂的顶层单端阻抗是SI8000无绿油模式算出来的值*0.9+3.2,但线宽,铜厚,PP板厚,芯板厚,介电常数都不是allegro中设得值。残铜量影响板厚。内层,负片层,外层同是1oz的铜,厚度完全不一样。

太迷惑拉。

求高手做八层以上的叠层,最好是做成allegro能用的。因为看到别的资料,说线的等长并不等于延迟的相等。而蛇线的唯一目地是为了延迟相等。不在allegro里设好叠层,延迟应该也是不准的吧。

好迷惑啊。

好在有一点,一般板要是做+/-10%误差的阻抗。这样就有一点,六层以下的普通板的阻抗,厂家都能满足。十层以上就难说拉

求有经验的详细来个例子流程

20%的误差,足够一般板不考虑阻抗拉