基于FPGA的信息安全系统设计

系统开发设计:

1.项目名称及主要内容

本项目名称是:基于FPGA的信息安全系统设计。

主要内容为:本模块采用xilinx公司的Spartan 3E系列XC3S500E型FPGA作为核心控制芯片,对采集到底模拟信号进行数字转换后通过3DES算法进行加密、然后通过网络传输,再经过解密算法解密出明文数据。尽管DES已被证实是不安全的算法(主要是密钥太短),但三重DES增加了密钥长度,由56位增加到112或168位,有更高的安全性,而且在新一代因特网安全标准IPSEC协议集中已将DES作为加密标准。利用3DES可以使原系统不作大的改动,所以对3DES的研究仍有很大的现实意义。在此使用了3DES算法,保证了系统功能的完整性与数据传输的安全性。该识别模块可用于国内外卫星通信、网关服务器、机顶盒、视频传输以及其它大量的数据传输业务中,也可和计算机等设备联机使用,满足各个方面的不同需求,因此它的设计具有很广泛的应用前景和市场价值。

2.项目关键技术及设计

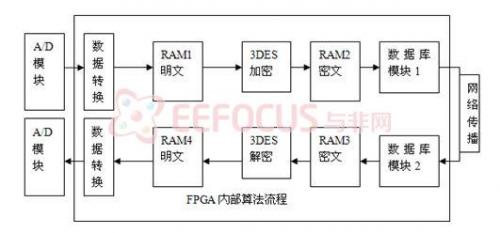

系统框图见下图

2.1 A/D、D/A模块

这两个模块功能是完成信号的转换功能,实现模拟信号与数字信号之间的转化。

2.3 数据加密(解密)

将转换好的明文数据存储在事先固化好的RAM1,基于3DES算法模块对明文进行加密,并将密文存储到RAM2中,并通过数据库技术连接到网络,通过网络传播,将传送后的密文数据采集到RAM3中,通过解密算法模块对密文解密存储到RAM4。

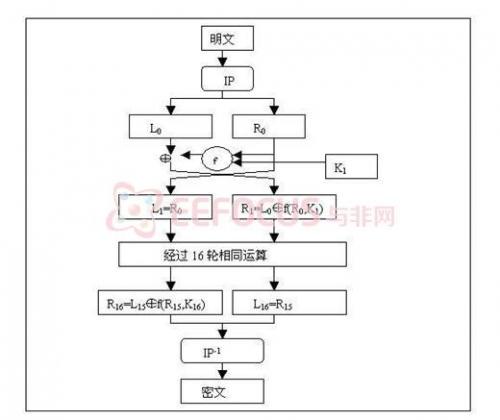

算法总体结构:通过一个密钥控制模块为3DES提供三个56位的密钥以及加/解密控制信号。密钥的输入是28位的,所产生的三个56位密钥并不是同一时间提供给3DES的,相互之间有16个时钟的延时,这样可以保证修改密钥后并不影响先前流水线的工作。再加上输入、输出接口就构成了该设计的总体结构,如图5所示。限于图的大小,不影响理解的部分信号没有画出。加/解密的流程是先输入六组28位的密钥,然后就可以发送需要加/解密的数据了,中间可以有间断,如果需要更改密钥,也是先输入改后的密钥,再输入数据,可实时更改,无需等到流水线中最后一组数据加/解密完成。

3 程序代码及仿真

3des部分代码

module des_3(key1, key2, key3, datain, sysclk, en, reset, mode1, mode2, mode3, load, ready, dataout);

input [64:1] key1;

input [64:1] key2;

input [64:1] key3;

input [64:1] datain;

input sysclk;

input en;

input reset;

input mode1;

input mode2;

input mode3;

input load;

output ready;

output [64:1] dataout;

wire flagwire1,flagwire2;

wire[64:1] datastream1,datastream2;

DES jia1(.sysclk(sysclk),.en(en),.reset(reset),.mode(mode1),

.load(load),.key(key1),.datain(datain),.dataout(datastream1),

.ready(),.flag(flagwire1));

DES jie(.sysclk(sysclk),.en(flagwire1),.reset(reset),.mode(mode2),

.load(load),.key(key2),.datain(dataistream1),.dataout(datastream2), .ready(),.flag(flagwire2));

DESjia2(.sysclk(sysclk),.en(flagwire2),.reset(reset),.mode(mode3), .load(load),.key(key3),.datain(datastream2),.dataout(dataout),

.ready(ready),.flag());

Endmodule

控制代码

module control(sysclk, reset, load, en, ready,

ct1,ct2,ct3,ct4,ct5,ct6,ct7,ct8,

ct9,ct10,ct11,ct12,ct13,ct14,ct15,ct16);

input sysclk;

input reset;

input load;

input en;

output ready,ct1,ct2,ct3,ct4,ct5,ct6,ct7,ct8,

ct9,ct10,ct11,ct12,ct13,ct14,ct15,ct16;

wire ready,ct1,ct2,ct3,ct4,ct5,ct6,ct7,ct8,

ct9,ct10,ct11,ct12,ct13,ct14,ct15,ct16;

D d1(sysclk,reset,en,load,ct1);

D d2(sysclk,reset,en,ct1,ct2);

D d3(sysclk,reset,en,ct2,ct3);

D d4(sysclk,reset,en,ct3,ct4);

D d5(sysclk,reset,en,ct4,ct5);

D d6(sysclk,reset,en,ct5,ct6);

D d7(sysclk,reset,en,ct6,ct7);

D d8(sysclk,reset,en,ct7,ct8);

D d9(sysclk,reset,en,ct8,ct9);

D d10(sysclk,reset,en,ct9,ct10);

D d11(sysclk,reset,en,ct10,ct11);

D d12(sysclk,reset,en,ct11,ct12);

D d13(sysclk,reset,en,ct12,ct13);

D d14(sysclk,reset,en,ct13,ct14);

D d15(sysclk,reset,en,ct14,ct15);

D d16(sysclk,reset,en,ct15,ct16);

D d17(sy

FPGA 信息安全系统 RAM IP核 乒乓操作 相关文章:

- 德州仪器推出具备n因数与串联电阻校正功能的+/-1℃远程与本地温度传感器(09-15)

- 基于FPGA的超声波液体密度传感器(07-05)

- 基于FPGA的司机眼球跟踪疲劳检测报警系统(07-05)

- 智能手机传感器管理,FPGA比AP+MCU方案功耗低10倍(10-11)

- 采用MEMS麦克风实现复杂环境下对特定语音的提取与放大(06-02)

- 多款陀螺仪表头设计、平台测试、系统研究方案及应用实例(06-28)