H.264视频解码芯片中与滤波相关的存储器的设计

为单位来进行传递。因此以block 为单位来进行数据的存取会带来很大的方便。本设计中各个SRAM 每一个地址存放一个block 单元的数据(16 个像素点),即采用128bit 的SRAM。

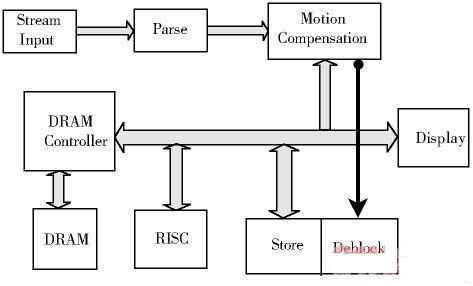

图3 DRAM 与其它模块之间的数据交互

在H.264 中运动补偿结束后的数据交由环路滤波运算后写入DRAM, 我们把写入DRAM 的这一过程称为Store 过程,由Store 模块负责。由图3 可以看出MC 与Deblock 是一个串联的关系。为了提高解码的速度,我们将运动补偿与环路滤波并行执行,即当前解码的结束并不以环路滤波的结束为标志,而当前宏块的运动补偿一结束我们就可以开始下一个宏块的解码。经过大量的实验发现:MC 的时间远比block的时间大很多,当后一个模块要进行滤波时滤波模块早已准备完毕。最后对存储模块我们也同样的用并行的思想来加快解码的速度。结果当作MBx 的MC 时,做MB(x-1)的滤波,同时MB(x-2)存储。此时需要注意MB(x-1)的滤波和MB(x-2)的存储并不是同时开始。因为做MB(x-1)的滤波时也会影响到MB(x-2)中的数据。

因此我们要等MB(x-1)的第一条垂直边滤波结束后才开始MB(x-2)的存储。具体的时间关系如图4 所示。

图4 各个模块之间的时序关系图

(1)滤波前数据的存储及滤波结束后数据的存储

由于设计中采用此种流程,我们需要3 片SRAM来存储MC 的运算结果。这3 片SRAM 交替地进行MC、Deblock 和Store。我们称这3 片SRAM 为SRAM_MB,滤波结束后的数据也存储在此SRAM 中,在经Store 模块将此数据存储到DRAM 中去。因为滤波结束时,恰好原来SRAM_MB 中的数据也已经成为无效数据。这里需要注意,由于有帧场自适应的情况存在,滤波结束后的数据如果帧场情况不一样,我们还需要根据数据不同的情况进行适当的帧场转化,之后再将数据存入DRAM。

(2)垂直滤波后的数据的存储

我们都知道滤波过程是一个先垂直后水平的过程,因此我们需要有一片SRAM 来存储水平滤波的结果。这片SRAM 就叫SRAM_BUFFER。因为水平滤波时正在从SRAM_MB 中读取数据,同一时间不能同时向SRAM 中读取、写入数据。因此我们用SRAM_BUFFER 来暂存垂直滤波结束后的数据。水平滤波时则从SRAM_BUFFER 中读取数据, 滤波后存储到SRAM_MB 中。

5 总结

本文对H.264 解码芯片中的滤波、存储模块作了深入的分析。并根据各个时间数据的特点作相应的存储器的设计, 这种设计方法经过验证能很好地处理H.264 中滤波及存储时的数据的调度。整个滤波过程约52 个周期就可以完成。在MBAFF 情况时各种数据的转化时钟周期控制在70 个以内。这种设计符合要求,并在FPGA 上验证后能够正常的运行,运行时钟达到60MHz,能实时地完成对高清图像的解码。

- 基于卡尔曼滤波器及多传感状态的融合估计算法介绍(06-30)

- 在PSpice中仿真数字滤波器的传输线设计(06-16)

- 信号链基础知识 #53 正确调节滤波器各组件以提高降噪效果(11-08)

- 航标遥测系统研究(01-05)

- MSP430F499的波形合成器(01-20)

- 用一个接地阻抗电流传感器重建输入电流(10-06)