基于单片机+CPLD的多路精确延时控制系统设计

时间:10-06

来源:国外电子元器件

点击:

4 系统软件设计 5 结语

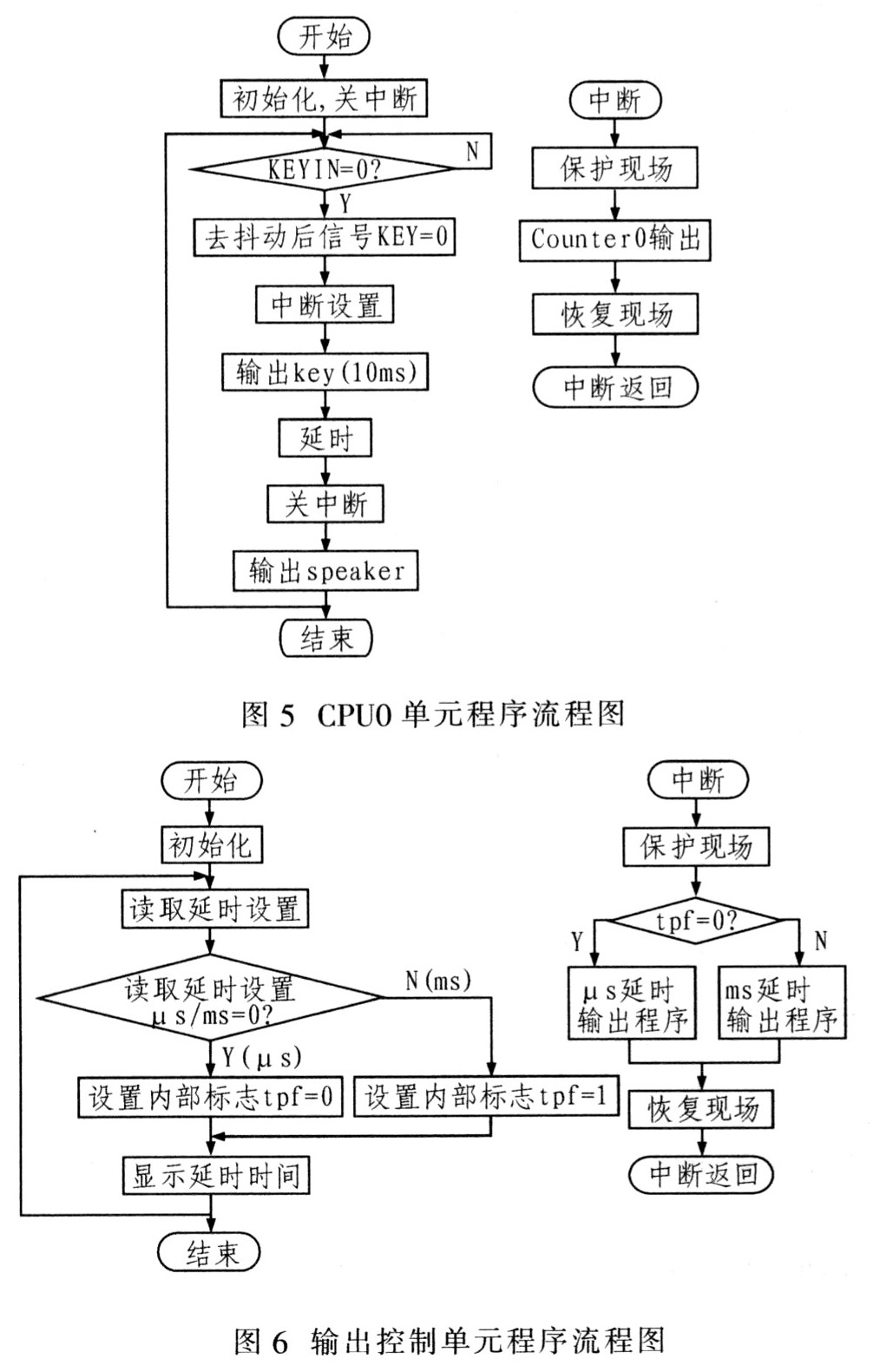

本系统软件设计包括CPUO单元、NO.1~NO.n输出单元及CPLD单元程序设计。由于对时间要求严格,采用汇编语言编写,信号输出由中断程序完成,由于中断响应过程、现场保护以及中断后必要的设置条件检测需要时间,所以软件必须通过容余指令(比如NOP)的延时,可保证counter0输出和控制信号延时起点在同一时刻。

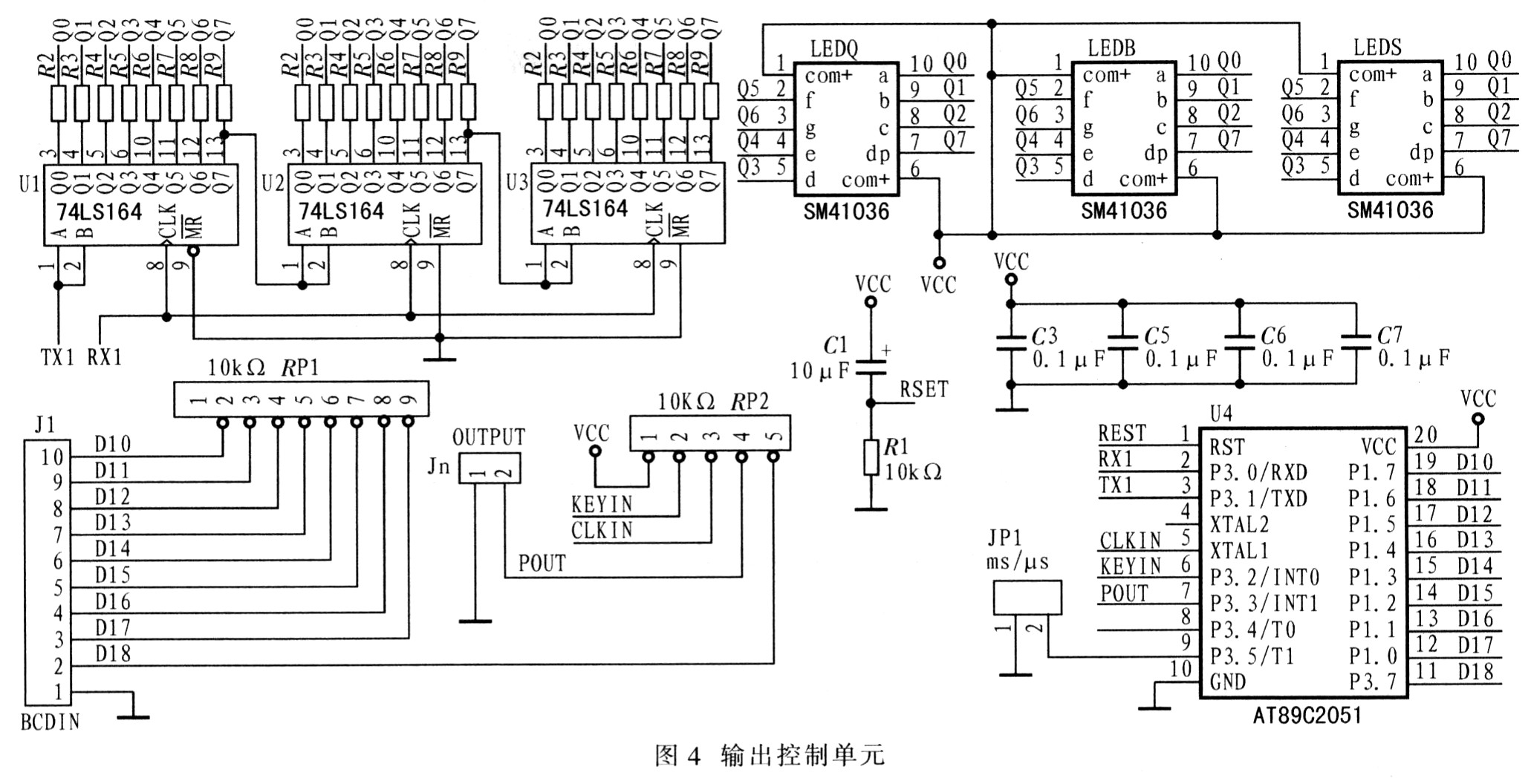

CPU0单元程序流程如图5所示。CPU0主程序完成系统初始化、按键检测、去抖动信号输出和工作状态提示音输出等工作,中断服务程序计时基准信号 counterO输出。输出控制单元NO.1一NO.n程序流程如图6所示,各单元主程序完成μs/ms设置检测,延时设置读取,延时时间显示,中断程序完成控制信号输出功能。CPLD程序采用VHDL语言编写,采用QHalftusⅡ软件编译仿真。

该系统设计可应用于电容组(9只)放电控制系统,在放电电子开关控制端、负载端测量以及微秒级延时范围内,延时误差小于O.1μs,毫秒级延时范围内,延时误差小于50μs。实际测试显示,系统实现了设计要求的调整精度。基于单片机+CPLD的多路精确延时控制系统充分利用单片机和CPLD的各自特点,实现主要设计指标。实际应用证明,该系统能够完全满足时序逻辑要求中严格控制系统的控制需求。

- 音量键上做指纹识别?Synaptics说到也做到了(01-19)

- 温度传感器TMP275在家庭环境监控中的应用(05-16)

- 5分钟搞定复杂系统电源配置 (07-23)

- 使用称重传感器注意事项 (11-15)

- 闭环霍尔电流传感器在车用电源系统中的应用(03-01)

- 智能红外遥控开关原理及设计(11-28)