超级接面功率MOSFET结构 有效提升系统效率和功率密度

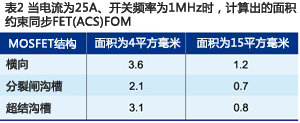

有最低的Sp.Rds(on)和CWS FOM,因而能够在所需芯片面积内发挥最佳性能。当采用更小的QFN3333封装时,这些技术均无法发挥其最佳性能(三者的ACS FOM>1)。然而,图4所示的结构中,明确标示出需要进一步降低Sp.RDS(on),尽管这样做可能导致开关FOM变差,详见分裂闸技术和横向技术针对面积小于4平方毫米应用的对比。

超级接面功率MOSFET损耗低

为展现超级接面功率MOSFET结构的优点,可对系统效率进行测量,并将测量结果与超级接面组件和芯片尺寸相似的场平衡结构组件做比较,工作频率为500kHz和1MHz、电压从12伏特转换为1.2伏特(图6)。当二者的芯片尺寸相同时,前者的导通状态损耗优于后者。当工作频率为500kHz和1MHz时,在30安培全负载和低负载条件下,系统效率均提高2%。超级接面芯片尺寸无论大小,均有可能出现下列情形,如重负载条件下的效率提升会牺牲轻负载效率,而轻负载条件的系统效率提升会牺牲重负载效率。采用RDS(on)较高的控制FET可能会改善效率,因为QGD降低所带来的益处大于RDS(on)升高所带来的坏处。

图6 超级接面技术与场平衡(FB)技术的效率测量结果对比,电压为12V转换至1.2V。

从上述中可知,控制FET的开关速度可能会受到QGD以外的其他因素限制。可从图7明显看出,低RDS(on)同步FET(PSMN1R2-30YLC)与中等RDS(on)同步FET(PSMN4R5-30YLC)的开关波形的比较。在这两个例子中,PSMN4R5-30YLC均作为控制FET。可明显地看出,开关节点(即控制FET和同步FET形成的半桥中点)的上升时间与控制FET无关。换言之,开关节点电压上升所导致的导通损耗不再受控制FET的QGD限制。

图7 PSMN4R5-30YLC和PSMN1R2-30YLC在导通和断开时的开关节点波形(即同步FET的VDS)

本例中的限制因素为电路通过寄生电感为同步FET的输出电容充电所需要的时间。结果显示使用者必须更加重视降低QOSS,而非CWS FOM隐含的值。断开操作是控制FET功耗最集中的时候,此时低RDS(on)和中等RDS(on) MOSFET的开关节点电压压降几乎是没有差别,这表示开关时间仍然受高侧组件的QGD影响。由于闸极电流比较低,且MOSFET闸极电阻具有内部分配性,控制FET的断开速度通常较慢于导通速度。因此控制FET极可能是决定组件断开时开关速度的影响因素。

在评估DC-DC转换的功率MOSFET性能时,不能仅考虑QG和QGD两个数值,因为近年来这些数值的降低,以致于必须考虑其他功耗机制。针对达成同步FET的性能优化,开发出两种新的FOM,分别是CWS FOM,综合了输出电荷效应(QOSS),以及考虑芯片尺寸限制的ACS FOM。

新的FOM被用于分析三种不同的功率MOSFET结构。结果显示最近开发的低压超级接面结构可完美结合低RDS(on)、低QG和低QGD等特性,其性能优于横向和分裂闸等竞争产品结构。此外,随着封装尺寸缩小,ACS FOM亦显示出在功率MOSFET设计中,牺牲Sp.RDS(on)以改善开关频率并非为最佳策略。

作者:Phil Rutter/Steven T Peake,恩智浦