使用QDR-IV设计高性能网络系统之三

时间:01-22

来源:3721RD

点击:

无ECC位的QDR/DDR SRAM的SER故障率(FIT)通常为200 FIT/Mb。但带有ECC时,该数值将为0.01 FIT/Mb,提高了4个数量级。

图11. 输出数据逻辑(x36器件)

QDR-IV存储器控制器的设计建议

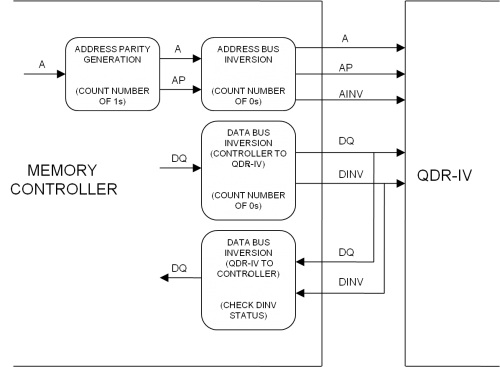

本节提供一些存储器控制器启用QDR-IV的地址奇偶校验和总线翻转功能的设计建议。

存储器控制器首先要根据地址总线生成地址奇偶。然后,需要在地址总线和地址奇偶位上进行地址翻转。

对于数据总线转换,将数据发送给QDR-IV前,存储器控制器需要计算每个DQ总线上的逻辑"0"的数量,以便生成相应的DINV位(取决于数据总线翻转条件)。

将数据发送给存储器控制器时,QDR-IV使用相同的数据总线翻转逻辑。为了识别QDR-IV的接收数据,控制器仅要检查相应DINV位的状态。如果控制器接收DINV = 1,需要翻转相关的数据总线;否则,保持接收到的数据位不变。

图12显示的是存储器控制器的设计注意事项。

图12. 存储器控制器的设计注意事项

结束语

QDR-IV提供2132 MT/s的最大RTR,是市场上性能最高的标准化解决方案。凭借较高的RTR外加两个双向端口、ECC、总线翻转、ODT、地址校验等差异化特性,它已成为网络系统的首选解决方案。QDR-IV的优势还适用于其它需要较高RTR和信号完整性的系统,如高性能计算和图像处理系统。

- 赛普拉斯的低功耗无线解决方案可助PURE 音频系统智能连接(05-12)

- AGIG采用最高密度、无需电池的非易失性RAM系统(09-23)

- 2010 FIRST机器人大赛选用赛普拉斯PSoC3 FirstTouch入门套件(02-13)

- 使用QDR-IV设计高性能网络系统之一(01-16)

- 基于QDR-IV SRAM实现高性能网络系统设计(01-16)

- 网络通信与便携式应用驱动SRAM技术(07-28)