利用SmartFusion2的SoC的数据采集与交互系统应用设计

0引言

Internet的快速发展和成功促进了以太网(Ethernet)技术的发展和应用的扩展,所涉及的领域十分广泛,如传统的工业控制、信息家电、智能家居、安全监控、楼宇自动化、医疗、环境监测等。大多数的数据采集设备的通信接口符合UART通信标准。这种通信方式的数据传输半径十分有限,并不能满足远距离传输的需求,并且不能接入Internet.因此数据的交互接入Internet就显得非常重要了。

1系统的总体方案及各主要模块设计

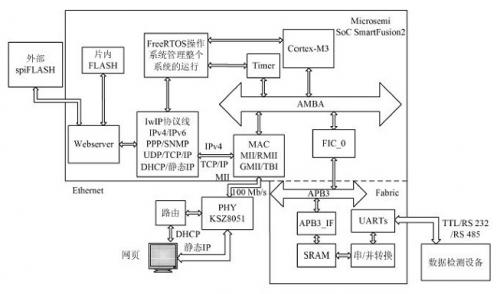

系统以Microsemi(Actel)公司的基于FLASH架构的SoC FPGA产品Smart Fusion2器件为核心。系统通过Fabric架构实现多路UART对外相应数据进行采集,进行并/串转换写入Fabric的双端口RAM.SmartFusion2的ARM Cortex-M3子系统经过AHB/APB总线矩阵以AHB/APB方式访问Fabric的RAM,将得到的数据经过Ethernet以网页的形式在PC上显示。反之,以同样的路径将主控的指令传输到外部的终端设备。PC机端以网页形式实现数据交互。网页存放于SmartFusion2内部FLASH,内核Cortex-M3基于实时操作系统(FreeRTOS)管理任务,IP采用静态方式,内核Cortex-M3与Fabric采用AHB方式通信[2-3].系统设计结构框图如图1所示。

图1 系统设计结构框图

系统硬件的设计可分为三个主要模块,分别为PHY物理层模块,SoC的Cortex-M3内核及FPGA系统,UART模块的数据采集系统。

1.1 PHY模块

PHY即物理层(Physical Layer)。物理层协议可定义电气信号标准、连线的状态、时钟信号的要求、数据编码的格式和数据传输所用的连接器等。物理层通过一个定义好的接口与数据链路层进行通信。比如MAC可以利用标准的介质无关性接口( MII接口)与PHY进行数据交换通信。PHY还有个重要的功能就是实现以太网的CSMA/CD部分功能,这是硬件上实现的。它可以检测到网络链路上是否有数据正在传送,如果有数据在传送中则进行等待,当检测到网络空闲,就再等待一定的时间(不同的PHY会有不同)后对数据进行传送。倘若两块网卡碰巧是同时发送数据,这将造成冲突,这时PHY内部的冲突检测结构可以检测到冲突的发生,然后两边各自等待一定的时间进行重发数据。

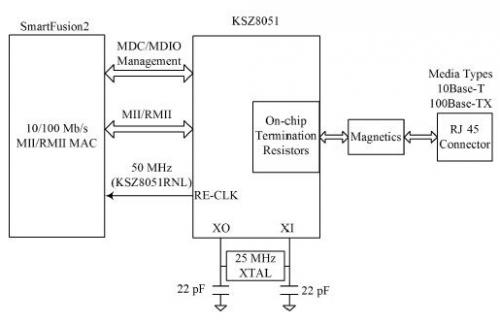

图2 PHY电路连接图

PHY的电路图连接图如图2所示。KSZ8051采用MII与SmartFusion2相连,由于MII兼容RMII接口,因此程序也可配置为RMII模式。Management采用2个引脚连接,分别为MDC和MDIO,MII的时钟由PHYKSZ8051提供,KSZ8051的时钟来自外部25 MHz晶振。媒体连接采用RJ 45,兼容10 Mb/s和100 Mb/s.

1.2 SoC中的Cortex-M3模块

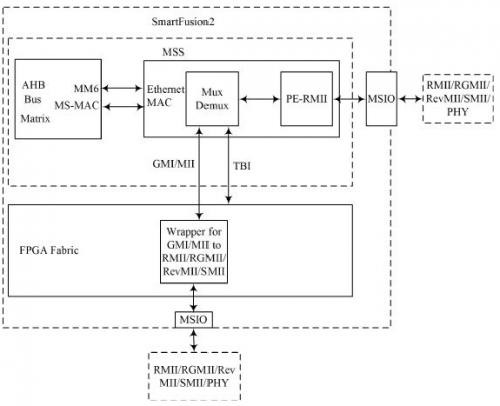

系统使用Cortex-M3中的MAC模块,如图3所示。

通过AHB控制Ethernet MAC模块,对于MAC的配置是使用其内部的寄存器,可以配置不同的接口模式,不同的速度。本系统配置为MII接口,100 Mb/s速度。

图3 Cortex-M3的MAC

MAC(Media Access Control,媒体访问控制子层协议),主要负责控制和连接物理层。在发送数据的时候,MAC协议可以事先判断现在是否可以发送数据,如果可以发送则将给数据加上一些控制信息,最终将数据及附带的控制信息以规定的格式发送到物理层;在接收数据的时候,MAC协议首先判断输入的信息是否发生传输错误,如果没有错误,则去掉控制信息发送至逻辑链路层(LLC)层。以太网MAC协议由IEEE 802.3以太网标准定义。

PHY与MAC的接口方式有多种,如:

MII,RMII,SMII,SSMII,GMII,SGMII,TBI等。目前常见的PHY都提供标准的MII接口,RMII信号是对PHY内部的MII的信号进行编码和解码,这就是说支持MII接口的PHY内部都含有RMII信号,也就是支持RMII接口。具体使用何种接口的PHY则必须根据MAC芯片对应的功能和接口的标准来决定。

采用FreeRTOS实时操作系统管理整个系统的运行。FreeRTOS使用Cortex-M3内核的定时器以10 ms时间片进行任务的调度和切换。创建WebServer进程和网页进行通信,网页编辑语言HTML是不需要编译的,因此将需要显示的数据全部发送给网页。这些数据存储在FLASH中,目前测试是存储在片内FLASH,网页发来的控制数据进行实时的处理。网页的数据需要用LwIP协议栈进行打包,LwIP协议栈是把所有的协议封装到一个单一的过程(进程)中,从而与操作系统内核分开。应用程序可能也驻留在LwIP处理过程中,或者在单独的过程中。TCP/IP栈和应用程序之间的通信可以通过函数调用实现,也可以通过更为抽象的API[4-5].本设计的应用层使用常用的IPv4协议,DHCP和静态IP都进行测试,传输层和网络层使用TCP/IP.

打包之后的需要介质层MAC进行处理,此MAC为Cortex-M3内核自带的,支持多种MAC接口,本设计采用MII接口,所采用的PHY芯片也是MII接口,采用Micrel公司的KSZ8051,支持MII、RMII接口,10 Mb/s和100Mb/s传输速度,设计时采用100Mb/s传输。

网页的数据需要实时更新,设计网页每隔500 ms发一次更新的命令,Cortex- M3再将更新的数据发送给网页。而这些数据来自APB3上,Cortex-M3通过FIC_0和APB3进行双向通信,从而发送和接收数据。FPGA中Fabric和APB3进行双向通信,数据存储在双端口SRAM中,多路UART和SRAM进行双向通信。SRAM在系统起缓存的作用,用来解决两端读写速度的不同。

而对于UART的数据也定义了协议,这些协议是区分数据的格式和内容。对于UART的个数可以进行增加,系统UART的同步使用FPGA硬件实现,不受个数的限制。

SmartFusion2 SoC Microsemi 数据采集 相关文章:

- SoC面临挑战,智能分割顺势而起(11-07)

- 基于PL3200的CDMA扩频电力线载波通信系统设计(11-19)

- 基于SOCKS地IPv4向IPv6过渡技术(01-08)

- 基于GPRS的SOCKET通信的应用研究(01-15)

- 蓝牙技术硬件实现模式分析(01-11)

- 代理服务器------代理之间的级联(03-17)