在蜂窝式无线电基础架构中实现软件可编程数字预失真

图4显示了C/C++的典型Vivado HLS高层次综合设计流程。该工具的输出为RTL,能够轻松地与现有硬件设计集成,例如数据路径预失真器或上游处理部分,当然还包括数据转换器接口。

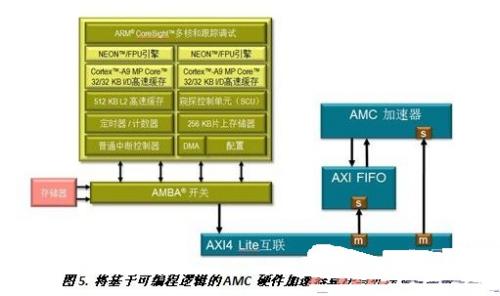

利用这种工具可以将算法快速移植到硬件,在这里算法必须通过AXI接口与PS连接,如图5所示。

在PL中以高时钟速率运行AMC算法能够显著提高性能(如图6所示),与在软件中实现相同的功能相比,可以实现70倍的性能提升,且只占用不到3%的AP SoC器件逻辑资源。

对原始C/C++参考代码进行基本的优化后,新代码在ARM A9处理器上的运行更加高效,将纯软件实现方案的性能提升至原始代码的至少2至3倍。此时,启用NEON媒体协处理器,可以获得额外的性能优势。图6的最终结果是通过在可编程逻辑中运行AMC算法(参见图5)获得的,其与最初的软件法相比,仅AMC功能就实现了高达70倍的总体性能提升。

最终是由无线电性能定义所需DPD在硬件与软件之间的分区。追求更高级别的频谱修正可以实现更高的效率,这可能会成为影响性能的一个因素。由于提高了用于表达放大器非线性的精确度,因而实现更高的修正水平需要更强大的处理能力。其他影响性能的因素是更大的传输带宽或在多个天线之间共享估算引擎。这种方式仅需一个处理器外加可选的硬件加速器即可为多个数据路径预失真器计算系数,从而实现面积(和成本)方面的节省。

在某些情况下,在ARM A9 + NEON单元上运行软件所获得的性能就足够了,例如窄带传输带宽配置,或在设计中只有1或2个天线路径需要进行数据处理的情况,这既可以减少无线电配置的面积也可降低成本。

为了将性能进一步提升至图6以上的水平,可为AMC功能的实现添加额外并行机制,但这需要以增加逻辑实现为代价才能缩短更新时间。此外,对软件进行更深入的分析可能会表明算法中其他可从硬件加速受益的部分。无论要求是什么,现在的工具和芯片都能帮助设计人员在追求更高效率的过程中轻而易举地在性能、面积以及功耗之间进行利弊取舍,而且不必受特定分立器件或编程风格的制约。

总结

无线电基础设施要求低成本、低功耗和高可靠性,而集成则是实现这些目标的关键,但直到现在也无法在不降低灵活性或减慢上市进程的前提下做到。此外,宽带无线电和对更高效率的追求正在促使处理要求不断提升。凭借双核处理器子系统、高性能和低功耗可编程逻辑优势,Zynq-7000 All Programmable SoC已成为能充分满足当前和未来无线电需求的解决方案。

无论是远程无线电设备还是有源天线阵列,设计人员都能以更高的生产力创建产品,同时实现比现有解决方案(如ASSP或ASIC)更高的灵活性和性能。软件与硬件之间的界限已不再清晰,这为需要更多高级算法以实现产品差异化的设计人员开启了无限可能性。

- GPRS与CDPD的技术比较(03-02)

- CDPD(蜂窝数字分组数据网)技术(03-08)

- 赛灵思和AXIS共同发布新型集成射频卡开发平台(11-20)

- 一种高效新型WCDMA 直放站PA 方案的设计与实现(02-28)

- TI GC5322 在CDMA中的应用(08-13)