基于FPGA部分动态可重构的信号解调系统的实现

传输来的配置数据,当出现部分重配置文件的结束标志DESYNCH(0000000D)时,就可以判断部分重构流程结束,可以运行新的重构模块。

3 基于FPGA部分动态可重构的信号解调系统开发流程

3.1 FPGA模块划分

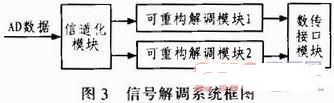

在完成了支持FPGA部分动态可重构的硬件实现后,下面开始规划信号解调系统的FPGA设计架构。如图3所示,信号解调系统主要由信道化模块,可重构解调模块和数传接口模块组成。

信道化模块主要是把AD数据进行信道化处理,进行滤波,下变频、信道选择和抽取。可重构解调模块是针对不同调制样式的分别实现不同的解调模块,并根据实际需要进行部分重构。数传接口模块是把解调的结果传输到FPGA外,进行后续处理和在界面中显示。

3.2 FPGA模块的设计和实现

按照图3所示的结构,按照下面步骤进行基于部分动态可重构技术的FPGA程序设计:

1)把需要部分重构的FPGA模块设计为一个空盒,即只有输入输出管脚,没有实际内容的空模块。在进行空模块的管脚规划时要综合考虑多种解调样式下的接口兼容性,保证一个模块接口能涵盖需要处理的所有样式。

2)分别完成不需要部分重构的FPGA予模块,并完成FPGA顶层模块。

3)对FPGA顶层模块进行综合,产生顶层网表。

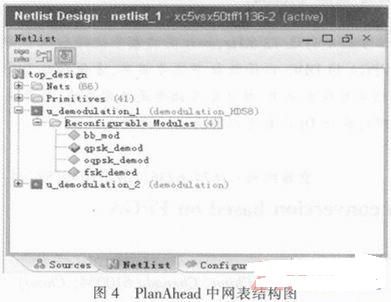

4)按照步骤1)中的模块定义格式完成针对不同调制模式的解渊模块,如qpsk_demod,fsk_demod等,并通过仿真验证,然后逐模块分别综合成单独的模块网表文件,保存到不同的目录中。

5)在PlanAhead工具中导入FPGA顶层网表,注意在导入选项中选择支持部分重构。在PlanAhead工具中把2个空的可重构解调模块设定为可重构分区(ReconfigurablePartition),如图4所示,并把步骤4)中综合好的模块网表指定为可重构模块下的可选内容。

6)在PlanAhead工具的Device视图中,对可重构模块划分分区(PBlock),目前分区只支持矩形,要求分区包含的资源数目略大于解渊模块所需资源的最大值,其中包括逻辑资源(查找表和寄存器),乘法器(DSP48E)和RAM资源。

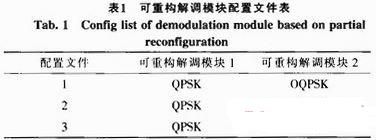

7)根据对2个可重构解调模块的不同配置,产生多个配置文件,配置文件的一个例子如表1所示,并逐一进行布局布线,产生完整的配置比特流文件和用于部分重构的比特流文件。对于每一组配置文件,会产生一个包含静态逻辑的完整配置比特流文件,和2个用于部分重构的比特流文件,分别对应2个不同的分区,配置加载时不能随便互换。

8)对表1中配置文件进行设计规则检查比较,保证各组配置文件生成的完整配置的比特流文件是一致的。

9)完成以上设计后,首先调用任意一个完整配置文件进行加载,保证FPGA成功运行静态逻辑,然后根据需要,选择表1中的配置文件表中的任何1组,进行部分动态加载。

4 应用结果

以上设计经过实际验证,可以实现2路信号在不同调制样式的解调,当信号样式变化时,动态加载相应的解调模块,可以迅速完成功能切换,实现对应的解调功能。经过实际测试,部分动态可重构模块的加载速度存10 ms以内,极大的提高了原有系统的性能。

5 结论

目前国际上对FPGA可重构技术的研究极为广泛,本文介绍了一种基于Xilinx FPGA的部分动态可重构技术的信号解调系统,可以把不同的解调模块定位到芯片内部同一逻辑资源部分,通过重构这些资源来实现不同样式信号的解调,同时保持其他部分电路功能正常运行,从而提高了系统的适应能力。

本系统可以存通信系统中得到应用,对航天、电力等领域的类似系统也有参考价值,可以提高相应系统的灵活性和扩展性,减低系统功耗,缩短系统开发时间。

- 一种基于电力线的家庭以太网络实现方法(10-10)

- 基于DSP和FPGA的机器人声控系统设计与实现 (04-16)

- 面向大众市场的千兆位级收发器(05-04)

- 利用以太网硬件在环路实现高带宽DSP仿真(05-04)

- 采用软处理器IP规避器件过时的挑战(05-04)

- WCDMA系统基带处理的DSP FPGA实现方案(01-02)