利用中端FPGA实现低成本网络

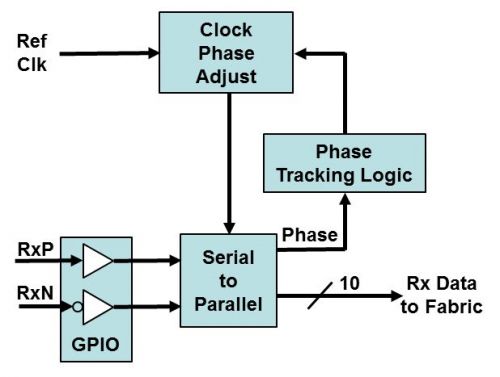

够将网络最边缘处具最低数据带宽需求的数据接口和网络中心区域及核心区段更高数据传输速率的接口汇聚在一起。边缘路由器、接入交换机和其他网络汇聚设备都同时支持低和高带宽数据速率。为满足数据汇聚的要求,中端FPGA不仅为下一代高速串行接口提供了一种经济的解决方案,还通过其增强的通用I/O(GPIO)功能支持传统的串行接口。利用GPIO来支持低端串行线速率,即1.25Gbps或更低,使得较昂贵的集成收发器通道可用于更高的串行线路速率。为支持串行接口,必须有一些时钟和数据恢复(CDR)逻辑,这是中端FPGA的另一个特点。图2提供了一个典型的CDR电路模块图。

图2:典型CDR电路模块图。

通过将硬化的时钟和数据恢复(CDR)逻辑合并到I/O结构中,再加上可访问选择硬化传输协议内核的PCS接口的结构,中端FPGA为各种不同的汇聚设备接口提供了串行线速率支持。

对设计人员而言,应用层逻辑是在FPGA中实现其解决方案时需要考虑的另一个因素。大多数传输协议都必须支持多种数据类型,每种都有其自己的传输模式、服务质量标准和控制平台要求。因此,硬化逻辑必须支持各种客户层协议语义。为提供最符合成本效益的和完整的解决方案,中端FPGA以软逻辑模块的形式提供这些不同的逻辑层接口。这些软逻辑模块为底层的传输协议模块提供了无缝接口,因为它们是整个协议栈的一部分,符合各自的行业标准。

另一方面,有时设计人员会认为专用的解决方案会更加适合,利用中端FPGA丰富的可编程逻辑功能,他们能够自由地设计最适合其要求的逻辑功能。但无论软逻辑层是专有的还是作为接口的一部分,建立一个完整的协议栈可能会很复杂,必须有一种简单的设计方法来帮助实现最终的解决方案。许多当今的中端FPGA可以使用图形化用户界面设计环境进行开发,这使得设计人员能够很容易地实现硬化逻辑的实例,并很快将它们与自己的逻辑块拼接在一起。设计人员可以在整个设计和实现阶段都使用这套软件工具,确保他们的串行接口能够正确地互连到自己的逻辑块,并且实例化的串行接口将能一次性运行成功。

本文小结

当前的接入网络由多样化的接口和逻辑处理单元组成。下一代网络需要处理和传输的数据与今天运营商所看到的数字相比将呈现几何数量级的增长。并且,当一个同构网络架构的传输压力越来越大,目前已安装的大多数设备根本就不能处理。因此,陈旧的设备与其较慢的器件接口必须和未来的高速接口和功能衔接起来。与此同时,还必须坚持严格的功耗预算、降低成本目标并缩短开发周期。

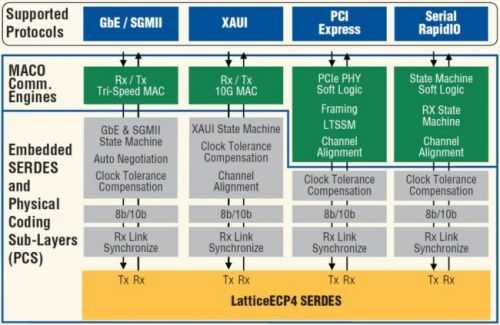

正如图3所示的LatticeECP4中端FPGA,它拥有可配置的收发器、硬化的行业标准传输协议块、丰富的可编程结构功能,以及图形化用户界面软件设计环境,为设计人员提供了开发下一代设备所需的功能来满足功耗和成本需求,并且延长了其原有设备的使用寿命。

图3:莱迪思中端FPGA硬化的协议逻辑。

- 一种基于电力线的家庭以太网络实现方法(10-10)

- 基于DSP和FPGA的机器人声控系统设计与实现 (04-16)

- 面向大众市场的千兆位级收发器(05-04)

- 利用以太网硬件在环路实现高带宽DSP仿真(05-04)

- 采用软处理器IP规避器件过时的挑战(05-04)

- WCDMA系统基带处理的DSP FPGA实现方案(01-02)