利用PCI局部总线实现BIade Server的数据交换

新一代机架式服务器Blade Server(刀片服务器),应用iSCSI协议,通过TCP/IP实现网络存储,利用Intemet,可将SCSI数据包传到地球上的任何地方。

笔者着眼于刀片服务器的内部构架和整体方案的介绍,主要论述了基于FPGA的刀片与主板之间PCI数据交换的具体实现方法。

1 刀片服务器系统构架

刀片服务器是一种HAHD(High Availability High Density,高可用高密度)的低成本服务器平台,是专门为特殊应用行业和高密度计算机环境设计的。每一块刀片均由"系统服务器主板+控制板"组成,可以远程启动Windows NT/2000、Linux、Solaris等操作系统。类似于独立的服务器,每块刀片可以没有独立硬盘来存储数据,而是多个刀片共享一个Raid磁盘阵列。在该模式下,每个刀片运行自己的系统,服务于用户指定的不同用户群,相互之间没有关联,不过也可以通过系统软件将这些刀片集合成一个服务器集群,在集群模式下,所有的刀片连接起来提供高速网络环境,实现资源共享,为相同的用户群服务。用户若需提高整体性能,只需在集群中插入新的刀片即可。刀片可热插拔,替换便捷,且维护时间减到最小。

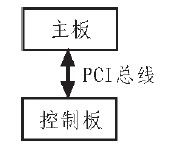

机架中的服务器(刀片)可以通过智能KVM转换板共享一套键盘、显示器和鼠标,以访问多台服务器(刀片),从而便于进行升级、维护和访问服务器上的文件。单个刀片通过PCI总线连接至主板,刀片中据的传输和交换,均通过该通道进行,刀片的实际组成如图1所示。

图1 刀片组成示意图

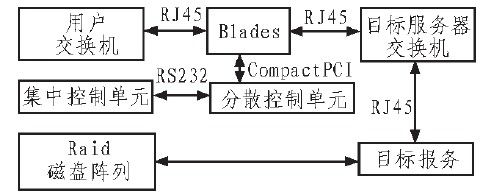

刀片在单机架系统中的位置如图2所示。

图2 刀片系统结构

在单机架系统中,用户交换机与Blade通过RJ45的千兆网接口进行连接,用户经用户交换机接入Blade服务器进行数据交换,可以在全球任何地方,由Intemet接入到用户交换机。集中控制单元具有网络端口等PC常用输出端口;分散控制单元(DMU)通过CompactPCI与Blade进行通信;通过232串口与集中控制中心(SMU)进行通信。DMU和SMU共同完成KVM的切换和采集Blade状态功能。

由于每个Blade没有单独的硬盘,所有Blade的启动都是通过目标服务器远程启动,并完成配置以及启动Raid中预装的操作系统,同时通过DHCPD(动态分配IP地址)、ADSS、iSCSI为每个Blade分配使用Raid磁盘阵列空间。也即每个Blade都是通过网络接口启动系统,所以网络配置要先于操作系统引导前完成初始化和驱动装载。

2 PCI局部总线概述

PCI总线是一种不依附于某个具体处理器的局部总线。从结构上看,PCI是在CPU和原来的系统总线之间插入的一级总线,具体由一个桥接电路实现对这一层的管理,并实现上下之间的接口以协调数据的传送。管理器提供了信号缓冲,使之能支持10种外设,并能在高时钟频率下保持高性能。PCI总线也支持总线主控技术,允许智能设备在需要时取得总线控制权,以加速数据传送。

通用PCI2.2接口信号如图3所示。在图3左半部分为必要信号,任选信号列于右边。其中信号名称右边加一个"#"符号表示是低电平有效,未加"#"符号的是高电平有效。根据信号的功能划分,可分为系统信号组、地址数据组、接口控制组、仲裁管理组、错误测试组、中断功能组、Cache支持组以及其他功能组。

图3 PCI局部总线引脚图

3 基于FPGA的PCI数据交换实现

通常PC都是采用本地硬盘来引导操作系统,完成设备的驱动,Blade则通过网络启动系统,所以网络配置要先于操作系统引导,并完成初始化和驱动装载。为了解决这个难点,我们采用"PCI+FPGA+Flash"结构,在Flash中烧录双端口千兆网卡PCI设备的初始化和驱动装载程序,由CPU在系统上电时加载Flash中的程序到系统内存。由于数据传输是PCI总线,而Flash是标准的数据总线,这就存在数据总线转换的问题,问题解决的方案是通过FPGA完成PCI设备与Flash之间的通信,下面将详细介绍如何利用FPGA来完成PCI接口和Flash之间的通信。

3.1 FPGA系统逻辑与实现

整个FPGA系统设计基于PCI2.2从设备设计思想,PCI主设备为PCI桥芯片,用FPGA来完成PCI从设备功能,终端为Flash芯片。在FPGA系统中,PCI总线接口部分的设计参数为:PCI时钟为33 MHz(CLK),32位I/O接口(AD[310]),终端接口可以提供20位或32位数据线。PCI主设备与终端Flash间的通信采用PCI从设备(FPGA)来实现的。在FPGA的逻辑设计中,终端是兼有Memory空间和I/O空间的抽象设备,在实际的设计中终端Flash,只有对应的memory空间。

根据FPGA的模块设计思想,采用Verilog语言将整个系统按功能进行分块设计,每个模块的输出可以为其他功能模块提供输入,各模块功能和设计思想如下:

"PCI顶层模块"是系统顶层模块,完成系统端口各使能开关的定义和调用其

- 基于混合TCP-UDP的HTTP协议实现方法(01-10)

- NGN在固网智能化改造中的引入与发展(01-09)

- 黑客实例讲解木马的分析方法! (01-16)

- 介绍几款黑客常用工具使用方法(01-23)

- NEC服务器应用于大学邮件系统(02-08)

- x86服务器虚拟化在数据中心遇到的8个问题(02-19)