基于SOPC的数据采集系统设计

。通过8位并行数据口D[0:7]和4位读写状态/控制口RXF、TXE、RD、WR就可实现与微控制器的数据交换。

3 FPGA系统硬件设计

Xilinx公司EDK(嵌入式开发套件)的XPS(平台工作室)的系统组建面板以展开式的树和表形式显示所有硬件平台IP实例,因此用户可以方便地查看自己的嵌入式设计。在此面板中可以对IP元素、端口、属性以及参数进行配置。

3.1 用户IP核设计

使用XPS进行基于MicroBlaze的用户IP核的开发,该套件集成了硬件平台产生器、软件平台产生器、仿真模型生成器、软件编译器和软件调试工具等。

为实现系统功能,需自定义一个IP核实现数据的采集与存储:该IP核包括五部分,分别为PLB总线接口模块、数据采集模块、数据缓存模块、数据存储模块FLASH读写控制逻辑。

(1)数据采集模块:利用FPGA逻辑资源实现A/D采集电路的控制逻辑。在功能上,该AD控制逻辑相当于一个主控制器。该控制过程无需处理器参与。另外AD控制逻辑与AD数据接口的分离,使得高速采集与发送数据成为可能。它连接两片12位的8通道MAXIM1308转换器,可实现多通道的数据采集。

(2)数据缓存模块:在FPGA内部设计FIFO将AD转换后的数据暂时存放其中。FIFO是Xilinx以FPGA片上Blockram为资源生成,FIFO模块的主要功能是数据缓冲,实现速率匹配。该异步FIFO模块在FIFO读、写控制模块的控制之下进行异步读写,FIFO的读时钟受数据存储模块控制,写时钟受数据采集模块的控制。FPGA内部设计了两片12位的FIFO与上述两片AD转换器相对应。

(3)数据存储模块:对本系统使用VHDL语言专门设一个DMA控制器来连接FIFO缓存和外部FLASH存储阵列。当FIFO缓存容量达到一定的值时可以启动DMA控制器建立一个高速的通道以提供连续的数据传输,存储到FPGA外部FLASH存储器阵列。这个通道使得只要FIFO缓存中的数据达到一定的值时便能迅速地存储到外部FLASH中,主设备不必为了确定从端口是否能够发送或接收数据而不断地访问从外设的状态寄存器。这使得系统的整体效率有了较大的提高,同时避免了自定义外设FIFO中的数据上溢或下溢。并且该过程只需要Microblaze处理器很少的干预即可完成,极大地节省了CPU资源。

(4)FLASH读写控制逻辑:主要实现K9XXG08UXA系列的NAND Flash存储器的读写时序,完成对FLASH的操作。

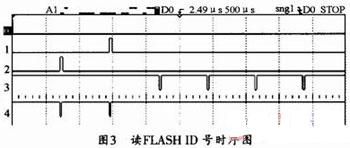

在SOPC硬件系统设计过程中用户IP核的设计是关键,它的设计是否成功决定着整个系统设计是否可行。在用户IP核设计过程中AD控制器、FLASH控制器、DMA控制器的设计都比较成功的,图3是对用户IP核设计的部分验证:示波器捕获的读FLASH存储器ID号时序图,且实验证明读出来的FLASH存储器的ID号是正确的。其中通道0-4分别代表FLASH的CE(片选)、ALE(地址锁存)、CLE(命令锁存)、RE(读)、WE(写)信号。

3.2 设计生成FPGA硬件系统

在XPS嵌入式开发环境中将用户IP核和标准总线核添加到系统中并将它们互相按规则连接起来。XPS提供了一个交互式的开发环境,允许用户对硬件平台各个方面进行设置。其中,XPS在高层对硬件平台描述进行维护,此高层形式即为微处理器硬件规范(MHS)文件。MHS文件作为一个可以编辑的文本文件,是表示用户嵌入式系统硬件部分的主要源文件。XPS将MHS文件综合到硬件描述语言网表中,用于FPGA的布局布线形成FPGA系统的硬件结构,该过程即是生成硬件比特流的阶段,形成后缀名为.bit的文件。

4 结束语

本文介绍了基于SOPC的多通道数据采集系统设计,可以对多种关心的环境参数进行采集并研究其特性。利用MicroBlaze微处理器搭建数据此采集与存储的嵌入式可编程片上系统,可以由单个芯片完成整个系统的主要逻辑功能。便于系统实现小型化,集成化。这种灵活的设计方式可随意扩展系统功能。在此基础上嵌入操作系统,可以进一步开发功能更强大的实时数据采集设备。

- 赛灵思和Xylon携手为嵌入式GUI系统开发推出灵活的低成本可编程logiTAP平台(01-12)

- 基于SOPC的高速数据采集系统的分析与设计(01-01)

- 基于SOPC的分布式干扰系统嵌入式网关设计(04-15)

- 基于电力线载波技术的系统设计(01-06)

- 双口RAM CY7C026在高速数据采集系统中的应用(04-12)

- 基于USB的运动控制平台及采集卡的设计(08-13)