FPGA在4G系统中的应用

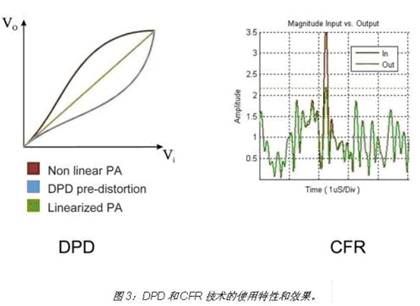

,因此使任何信号失真无效,这是功率放大器的特性导致的。在射频输出功率大于1~2瓦的大功率系统中,它通常与CFR相结合。这些技术的使用特性和效果如图3所示。

在RRU中使用CFR 和 DPD技术,可以让系统工程师使用比采用其他技术更低成本的功率放大器。这两种方法都需要大量的DSP处理功能,以实现行必要的算法。最重要的是,它们还要求一定的可适性,因为它们需要适应功率放大器传输特性的任何变化,这种变化可能发生在温度和时间变化的情况下。

RRU内远程无线处理器的合并是对这个问题的解决方案之一。传统上,ASIC被广泛用于蜂窝基站的设计,但是它们的设计周期长、固定成本高且不灵活,不适合仍在不断发展的市场。对于这个问题,分立的DSP处理器似乎是另一个解决方案,但分析表明,在多种标准的基站实现方面,它们也有局限性。另一方面,具有嵌入式DSP单元、SerDes功能和软处理器的FPGA在一个可重构的芯片中提供所有的功能。这个器件就是莱迪思半导体公司的ECP3。对任何带有SERDES功能的FPGA器件而言,这个FPGA具有业界最低的功耗和价格。该系列产品提供遵守XAUI抖动标准的多协议3.2G SERDES、DDR1/2/3存储器接口、功能强大的DSP功能和高密度的片上存储器。与带有SERDES功能的FPGA相比,所有这些功能只需竞争产品的一半功耗和一半价格。

不过,在选择FPGA时必须要认真考虑,以满足系统的物理和性能参数要求。获得实现RRU的关键功能的IP核,对整个系统的解决方案而言至关重要。作为IP合作伙伴计划的一部分,莱迪思公司与拥有丰富蜂窝无线系统经验的Affarii公司一起致力于该项工作。LatticeECP3 FPGA 与Affarii的IP结合在一起,提供了一个灵活的平台,可以在FPGA架构中组合构建RRU所需的所有IP模块。

针对发送和接收,RRU处理器的功能是多路复用和调制这个信号数据到射频载波。图4给出了莱迪思的IP和Affarii提供的IP。这些块用不同的颜色加以区别。

针对不同的具体应用,可以对CFR配置进行优化。最高载波配置的模拟可以决定精确的参数。在设计工具和文档提供了标准的系统配置,对于用户自己的应用,用户还可以创建自定义的配置,使用IP模型和有IP核的仿真环境。将CFR IP放置在LFE-70E FPGA中进行布局和布线,资源利用率如表1a所示。

通过针对功率放大器的特性来确定DPD工作的配置是最好的方法。DPD核本身支持诊断接口,以提供现场或测试源的数据分析。使用这个工具,可以实现放大器的非线性复杂特性,因此可以针对DPD决定最好的配置。因为它测量实时的放大器参数,这个过程还可突出显示在设计放大器时所需作出的改进。表1b给出了将DPD放置在Lattice LFE-70EP中进行布局和布线所需的资源。

该Affarii IP不仅包括了CFR和DPD功能,而且还有DUC、DDC和匹配引擎的功能,这是基站结构的重要组成部分。

由莱迪思提供的主要IP块是CPRI和OBSAI。这些是使用FPGA中带有的嵌入式SERDES功能的高速接口,连接远程基带至RRU。以太网MAC提供监测和控制系统的功能。设计师也可以选择使用LatticeMico32软微处理器用于RRH通用处理和控制,以减少元件的数量和节省成本。用先进的存储器接口和通用I / O(GPIO)接口可以完成该系统。

本文小结

FPGA现在已发展成为高度集成的器件,可以包括嵌入式ASIC类型的功能,提供增强的接口功能。软微处理器功能加上DSP处理器和嵌入式存储器,意味着在基站设计中使用的FPGA,将用一个可重构芯片提供功能核。可编程器件提供的优点将使产品能够更快地进入市场,灵活地适应新标准和不断发展的具有成本效益的标准。

- 一种基于电力线的家庭以太网络实现方法(10-10)

- 基于DSP和FPGA的机器人声控系统设计与实现 (04-16)

- 面向大众市场的千兆位级收发器(05-04)

- 利用以太网硬件在环路实现高带宽DSP仿真(05-04)

- 采用软处理器IP规避器件过时的挑战(05-04)

- WCDMA系统基带处理的DSP FPGA实现方案(01-02)