采用FPGA和DSP直接控制硬盘实现存储控制的方法

时间:02-07

来源:EDN

点击:

|

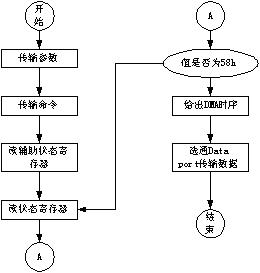

图4 DMA操作流程图 5 设计中的重点 5.1 采样率问题 数据采集及存储系统一般都有采样率要求,采样率一般要求大于50K,才能满足快速实时采集数据的要求。本系统中速度较慢的环节是硬盘存储环节,硬盘接口设计存盘速度为7.8Mbyte/S,显然采集速率与存盘速率并不匹配,解决的措施为采用一片 FIFO作为数据缓冲区。由于对硬盘操作过程中,需不断查询其状态,而硬盘状态改变时间又不确定,所以要选用存储深度较大的FIFO作为缓存,IDT公司的72V2101满足设计要求[5]。工作时数据直接将数据写入FIFO,FPGA查询FIFO的状态,为非空时,协调DSP访问硬盘,进行存储操作,这样采用FIFO作为缓存的方案解决了速率匹配问题[4],当采样率为80k时,数据流为5Mbyte/S,本系统设计存盘速度为7.8Mbyte/S,可以满足80K以内数据采样率系统的存盘要求。 5.2 硬盘存储地址问题 硬盘中数据如何存储是本设计中另一个重点问题,主要考虑文件存储的地址及文件目录情况。本设计中硬盘文件的存储采用FAT32文件系统,引导扇区记录了文件分配表的地址、个数、大小、簇的大小等信息。文件逻辑地址=数据段起始地址+(簇号- RootClus)×SecPerClus;数据段起始地址=BPB地址+RsvdSecCn+FATSz32×NumFATs。)文件目录设计采用短文件名,每个文件名和相关信息占用32字节,每个磁盘第2簇为目录区,因使用短文件名无子目录,所以当每簇为16扇区时目录区共可储存256个文件名。 6 结束语 本系统数据存储量较大,较传统使用工控机进行数据存储功耗较低,适合于工作环境局限、系统要求具有自动内记功能的工况下。本系统已经应用于某信号采集设备中,实践证明可满足使用要求,系统工作稳定,没有数据溢出现象。当然本系统还有一定不足,如不能存储任意长度数据文件,只能存储40M长度文件,还需进一步完善。 发布者:博子 |

- 一种基于电力线的家庭以太网络实现方法(10-10)

- 基于DSP和FPGA的机器人声控系统设计与实现 (04-16)

- 面向大众市场的千兆位级收发器(05-04)

- 利用以太网硬件在环路实现高带宽DSP仿真(05-04)

- 采用软处理器IP规避器件过时的挑战(05-04)

- WCDMA系统基带处理的DSP FPGA实现方案(01-02)