大容量闪存器件K9KAG08UOM与DSP的接口设计

时间:01-04

来源:EDN

点击:

前言

惯性导航系统、各种导引头及空间飞行器等测试和记录应用系统,都需要自主、实时、可靠存储大量的关键信息,并保证即使整个系统掉电,所采集到的数据仍能长时间保持不丢失,实现历史数据查询,便于数据分析。NAND Flash闪速存储器(简称闪存)以其掉电非易失、功耗低、寿命长、容量大、升级容易等独有的特点迅速成为数据存储的最佳选择。

某型激光陀螺惯导单元需要在湖试和海试试验过程中记录大量导航参数,为了便于在试验结束后有效分析数据。这里提出一种基于大容量闪存器件K9KAG08UOM与DSP的接口设计方案。在激光惯导的计算机板上集成了一片NAND Flash闪速存储器,根据试验的次数和每个航次存储数据量的大小,选用SAMSUNG公司的K9KAG08UOM存储器;为满足导航控制的周期和算法的复杂程度,选用TI公司的浮点DSPTMS320C6713B作为主控处理器。TMS320C6713B的主频可达300 MHz,浮点运算速度可达1.8 GFLO/S,是目前运算速度最快的浮点器件之一,已成为嵌入式系统设计中的主流处理器。其中NAND Flash与DSP的接口设计是整个计算机板设计的关键部分,这里详细介绍大容量NAND Flash与DSP接口设计的硬件接口电路和软件实现方法。

2 大容量闪存K9KAG08UOM简介

K9KAG08UOM是大容量、高可靠性的NAND Flash存储器。其存储容量为2 G字节(2 Gx8 bit);可将数据线与地址线复用为8条I/O线。并分别提供命令控制信号线;命令、地址和数据信息均通过8条I/O线传输,不会因存储容量的增加而增加引脚数,从而极大方便系统设计和产品升级,而无需更改外部硬件连接,因此成为嵌入式系统中实时存储大容量数据的最佳选择。

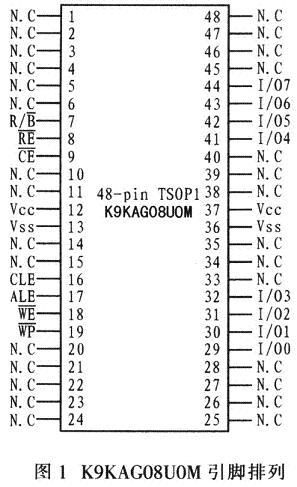

K9KAG08UOM引脚排列如图1所示,其引脚功能如下:

I/O0~I/O7:8根地址、数据和命令复用信号。用于输入命令、数据、地址及输出数据。

CE:片选信号。用于选择控制器件。

WE:写使能信号。通过该端口可在写脉冲的上升沿锁存指令、地址和数据。

RE:读使能信号。在读信号的下降沿,输出数据有效,并可累加其内部数据地址。

CLE:命令锁存使能信号。CLE为高电平时,命令通过I/O端口线在写信号的上升沿被锁存入命令寄存器。

ALE:地址锁存信号。在写信号的上升沿且地址锁存信号为高电平时,地址被锁存。

WP:写保护信号。WP为低电平时,禁止写或擦除操作。

R/B:准备就绪或忙输出显示信号,当R/B为低电平时,表示有编程、擦除或随机读操作正在进行,操作完成后.R/B信号自动返回至高电平。

3 硬件接口设计

3.1 计算机板设计方案

激光陀螺惯导计算机板以CPU为核心,完成数据的采集、运算、通信、数据存储等任务。计算机板的设计原理如图2所示。

计算机板主要包括:核心CPU完成导航计算及对外围接口的管理与控制等:监控与导航Flash完成程序的自主加载引导;NAND Flash完成试验数据的记录与下载;FPGA辅助完成A/D转换时序控制、总线译码控制、开关电路控制、分频及脉冲计数等功能:4通道串行控制器 TL16C754控制4个通道串口。

主机CPU选用DSP器件 TMS320C6713B,其内含浮点数值处理器,支持64位浮点运算,内部RAM容量为256 K字节,主频最高可达300 MHz,带有的锁相环电路使其能够通过软件编程设置实际工作频率。

根据系统时序控制和计数等功能需要逻辑门的大小.FPGA选用ACTEL公司的APA300。该器件内部自带ROM,上电后自主运行,无需外部ROM引导,可靠性高。

串行通信控制器选用,TI公司的TL16C754B。该器件采用3.3 V供电,功耗低,内部有4个并行的串行通信控制器,内部白带FIFO模式,与DSP无缝接口,使用灵活方便,满足系统设计需要。

3.2 NAND Flash与DSP硬件接口设计

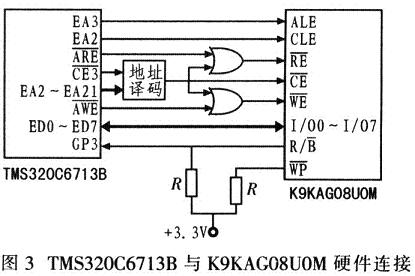

大容量闪存NAND Flash与DSP之间的接口设计是CPU板设计的关键。DSP主要通过EMIF外部存储器接口访问片外存储器,TMS320C6713B可与大多数的同步存储器和异步存储器灵活配置,使用简单方便。TMS320C6713B与K9KAG08UOM的硬件接口电路如图3所示。

TMS320C6713B的外部存储器接口包括:20位地址线、32位数据线、4个片选控制线及读写控制信号线。4个片选信号分别对应4个存储空间,CE3对应的地址空间为OxB0000000-OxBFFFFFFF,设计中通过地址译码实现地址空间的分隔,其中大容量闪存器件K9KAG08UOM的片选面对应的地址为OxB0400000。

K9KAG08UOM无地址线,命令、地址和数据信息均通过I/00~I/07传输。虽然K9KAG08UOM的容量达到2 G字节,远远超出TMS320C6713B存储区域CE3的可寻址容量256 M字节,但由于访问NAND Flash的地址是通过I/O端口输入,无需通过地址线寻址,因此不用考虑逻辑存储空间与实际物理空间的映射问题,简化了DSP与NAND Flash的硬件接口。

TMS320C6713B和K9KAG08UOM的工作电压均是3.3 V,因此两者引脚可直接连接,无需电平转换。设计中K9KAG-08UOM的ALE和CLE两个信号分别由DSP的最低两位地址EA3和EA2控制。DSP的低8位数据线直接与NAND Flash的I/00~I/07相连。DSP的通用输人输出端口GP3接R/B,用于监测NAND Flash的工作状态。当R/B处于低电平时,表示有编程、擦除或随机读操作正在进行;当R/B处于高电平时,表示操作已经完成。K9KAG08UOM的读写控制信号RE和WE由DSP的读写控制信号ARE和AWE和译码产生的片选信号CE通过逻辑或得到,只有当DSP的读写控制信号和片选同时有效即为低电平时才能对K9KAG08UOM进行读写操作。

该硬件接口设计利用DSP的地址线EA3、EA2分别控制NAND Flash的命令锁存ALE和地址锁存CLE信号,此时对K9KAG08UOM的访问相当于访问地址分别为OxB0400002、OxB0400001和OxB0400000的3个端口.分别对应K9KAG08UOM的地址端口、命令端口和数据端口。DSP对K9KAG08UOM的命令、地址和数据操作可通过不同端口进行。简化了对K9KAG08UOM读写控制和软件编程设计的难度。

惯性导航系统、各种导引头及空间飞行器等测试和记录应用系统,都需要自主、实时、可靠存储大量的关键信息,并保证即使整个系统掉电,所采集到的数据仍能长时间保持不丢失,实现历史数据查询,便于数据分析。NAND Flash闪速存储器(简称闪存)以其掉电非易失、功耗低、寿命长、容量大、升级容易等独有的特点迅速成为数据存储的最佳选择。

某型激光陀螺惯导单元需要在湖试和海试试验过程中记录大量导航参数,为了便于在试验结束后有效分析数据。这里提出一种基于大容量闪存器件K9KAG08UOM与DSP的接口设计方案。在激光惯导的计算机板上集成了一片NAND Flash闪速存储器,根据试验的次数和每个航次存储数据量的大小,选用SAMSUNG公司的K9KAG08UOM存储器;为满足导航控制的周期和算法的复杂程度,选用TI公司的浮点DSPTMS320C6713B作为主控处理器。TMS320C6713B的主频可达300 MHz,浮点运算速度可达1.8 GFLO/S,是目前运算速度最快的浮点器件之一,已成为嵌入式系统设计中的主流处理器。其中NAND Flash与DSP的接口设计是整个计算机板设计的关键部分,这里详细介绍大容量NAND Flash与DSP接口设计的硬件接口电路和软件实现方法。

2 大容量闪存K9KAG08UOM简介

K9KAG08UOM是大容量、高可靠性的NAND Flash存储器。其存储容量为2 G字节(2 Gx8 bit);可将数据线与地址线复用为8条I/O线。并分别提供命令控制信号线;命令、地址和数据信息均通过8条I/O线传输,不会因存储容量的增加而增加引脚数,从而极大方便系统设计和产品升级,而无需更改外部硬件连接,因此成为嵌入式系统中实时存储大容量数据的最佳选择。

K9KAG08UOM引脚排列如图1所示,其引脚功能如下:

I/O0~I/O7:8根地址、数据和命令复用信号。用于输入命令、数据、地址及输出数据。

CE:片选信号。用于选择控制器件。

WE:写使能信号。通过该端口可在写脉冲的上升沿锁存指令、地址和数据。

RE:读使能信号。在读信号的下降沿,输出数据有效,并可累加其内部数据地址。

CLE:命令锁存使能信号。CLE为高电平时,命令通过I/O端口线在写信号的上升沿被锁存入命令寄存器。

ALE:地址锁存信号。在写信号的上升沿且地址锁存信号为高电平时,地址被锁存。

WP:写保护信号。WP为低电平时,禁止写或擦除操作。

R/B:准备就绪或忙输出显示信号,当R/B为低电平时,表示有编程、擦除或随机读操作正在进行,操作完成后.R/B信号自动返回至高电平。

|

3 硬件接口设计

3.1 计算机板设计方案

激光陀螺惯导计算机板以CPU为核心,完成数据的采集、运算、通信、数据存储等任务。计算机板的设计原理如图2所示。

|

计算机板主要包括:核心CPU完成导航计算及对外围接口的管理与控制等:监控与导航Flash完成程序的自主加载引导;NAND Flash完成试验数据的记录与下载;FPGA辅助完成A/D转换时序控制、总线译码控制、开关电路控制、分频及脉冲计数等功能:4通道串行控制器 TL16C754控制4个通道串口。

主机CPU选用DSP器件 TMS320C6713B,其内含浮点数值处理器,支持64位浮点运算,内部RAM容量为256 K字节,主频最高可达300 MHz,带有的锁相环电路使其能够通过软件编程设置实际工作频率。

根据系统时序控制和计数等功能需要逻辑门的大小.FPGA选用ACTEL公司的APA300。该器件内部自带ROM,上电后自主运行,无需外部ROM引导,可靠性高。

串行通信控制器选用,TI公司的TL16C754B。该器件采用3.3 V供电,功耗低,内部有4个并行的串行通信控制器,内部白带FIFO模式,与DSP无缝接口,使用灵活方便,满足系统设计需要。

3.2 NAND Flash与DSP硬件接口设计

大容量闪存NAND Flash与DSP之间的接口设计是CPU板设计的关键。DSP主要通过EMIF外部存储器接口访问片外存储器,TMS320C6713B可与大多数的同步存储器和异步存储器灵活配置,使用简单方便。TMS320C6713B与K9KAG08UOM的硬件接口电路如图3所示。

|

TMS320C6713B的外部存储器接口包括:20位地址线、32位数据线、4个片选控制线及读写控制信号线。4个片选信号分别对应4个存储空间,CE3对应的地址空间为OxB0000000-OxBFFFFFFF,设计中通过地址译码实现地址空间的分隔,其中大容量闪存器件K9KAG08UOM的片选面对应的地址为OxB0400000。

K9KAG08UOM无地址线,命令、地址和数据信息均通过I/00~I/07传输。虽然K9KAG08UOM的容量达到2 G字节,远远超出TMS320C6713B存储区域CE3的可寻址容量256 M字节,但由于访问NAND Flash的地址是通过I/O端口输入,无需通过地址线寻址,因此不用考虑逻辑存储空间与实际物理空间的映射问题,简化了DSP与NAND Flash的硬件接口。

TMS320C6713B和K9KAG08UOM的工作电压均是3.3 V,因此两者引脚可直接连接,无需电平转换。设计中K9KAG-08UOM的ALE和CLE两个信号分别由DSP的最低两位地址EA3和EA2控制。DSP的低8位数据线直接与NAND Flash的I/00~I/07相连。DSP的通用输人输出端口GP3接R/B,用于监测NAND Flash的工作状态。当R/B处于低电平时,表示有编程、擦除或随机读操作正在进行;当R/B处于高电平时,表示操作已经完成。K9KAG08UOM的读写控制信号RE和WE由DSP的读写控制信号ARE和AWE和译码产生的片选信号CE通过逻辑或得到,只有当DSP的读写控制信号和片选同时有效即为低电平时才能对K9KAG08UOM进行读写操作。

该硬件接口设计利用DSP的地址线EA3、EA2分别控制NAND Flash的命令锁存ALE和地址锁存CLE信号,此时对K9KAG08UOM的访问相当于访问地址分别为OxB0400002、OxB0400001和OxB0400000的3个端口.分别对应K9KAG08UOM的地址端口、命令端口和数据端口。DSP对K9KAG08UOM的命令、地址和数据操作可通过不同端口进行。简化了对K9KAG08UOM读写控制和软件编程设计的难度。

NAND Flash DSP 存储 接口 ARM 相关文章:

- 基于GPRS的远程心电实时监护仪软件系统设计(02-10)

- 如何选用合适的闪存进行设计?(05-24)

- 基于ARM9内核Processor对外部NAND FLASH的控制实现(07-12)

- Cypress推出首款多媒体手机专用外设控制器(11-11)

- 基于ARM9的USB设计与实现(07-03)

- 基于VxWorks的NAND FLASH驱动程序设计(07-31)