基于加密USB2.0接口芯片的设计及验证

时间:11-12

来源:21IC

点击:

0 引言

USB 总线因其具有高速度、即插即用、功耗低等特点,深受广大用户的青睐。但USB 规范本身并未考虑数据传输时的安全性问题,所以它的安全性能低,不适合用来传输安全性 要求较高的信息。本文在研究USB2.0 规范以及应用密码学等安全防护技术的基础上,提出 一个基于ASIC 的整体解决方案。目的是用硬件描述语言设计一个既符合USB2.0 规范,同 时又可以将流经该接口芯片的数据进行自动加密的专用集成电路。最后,对所设计的系统在 FPGA 上进行验证,给出系统在FPGA 上所耗用的资源以及性能参数,对得到的数据进行分 析。

1 相关知识

1.1 USB 简介

从USB1.0 版本发布到2.0 版本,中间经历了多次版本更新。从1998 年7 月的Windows98 开始,USB 外围设备开始陆续出现,同时也成为最受欢迎的接口.它的优点为:容易使用、 传输速度快、低价位、低能耗、高稳定性、操作系统支持、外围设备的支持、有弹性.缺点 为:缺乏对数据安全性的考虑、缺乏对旧硬件的支持、点对点的通信、速度的限制、距离的 限制、硬件的错误或故障、协议的复杂性、版权费。

1.2 AES 简介

1.2.1 原理及起源

AES(Advanced Encryption Standard)是由美国国家标准与技术研究所于1997 年提出征集 该算法的公告并最终选定了两个比利时研究者Vincent Rijmen 和Joan Daemen 发明的 Rijndael)算法,并于2001 年正式发布了AES 标准。

1.2.2 AES 工作流程

Rijndael 算法本质上是一种对称分组密码体制,采用代替/转换网络,每轮由三层组成: 线性混合层确保多轮之上的高度扩散;非线性层由16 个S 盒并置起到混淆的作用;密钥加 密层将子密钥层异或到中间状态。Rijndael 是一个迭代分组密码,其分组长度和密钥长度都 是可变的,只是为了满足AES 的要求才限定处理的分组大小为128 位。而密钥长度为128 位、192 位或256 位,相应的迭代轮数Nr 为10 轮、12 轮、14 轮。可以抵御强大和实时的攻击。

2 系统解决方案

2.1 系统原理

本文主要目的是要设计一个既符合USB2.0 规范的数据接收和发送,又可以对接收到的 数据进行自动加密的专用集成电路的设计,并将所设计的系统用FPGA 对其进行功能验证。

该系统由两大模块组成:USB 模块和AES 加密模块。 系统结构如图1 所示:

其中,USB 模块实现流经数据依照USB2.0 规范进行接收和发送。将要发送的数据进行装配、 打包处理,并对接收到的数据包进行分解,在存储器接口与优先级判别模块的处理之后将数 据存入外部存储器 (SSRAM)或通过WISHBONE 接口电路与外围设备进行通讯;AES 加密 模块负责对接收到的数据进行加密处理,密钥封装在芯片中的存储器中。

2.1.1 USB 接口模块原理

该模块实现了符合USB2.0 规范的数据处理以及不同的外设与计算机的互连和数据通 信。 该模块的主要功能包括:

(1) 完全支持 USB2.0 规范,提供全速模式和高速模式,其数据率分别为12Mbit/s 和 480Mbit/s。

(2) 支持 WISHBONE 接口电路和该模块之间采用DMA 方式进行数据通信。

(3) 模块的挂起/恢复功能。 该模块结构如图2 所示。其中。PHY 模块负责将数据发送到与USB 连接器相连的计算 机,或接收来自计算机的数据;UTMI(数据通用收发宏单元接口)与PL(协议层)模块及内部 数据存储器、控制寄存器相连负责保持通信数据的格式符合USB2.0 规范中的协议格式; WISHBONE(主接口电路)是内部数据存储器、控制寄存器与外部设备之间的通信桥梁。

2.1.2 AES 模块原理

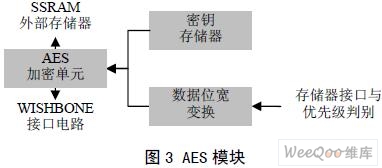

该模块负责将USB 模块接收并解包的数据进行加密然后将加密后的数据存入外部存储器或通过WISHBONE 接口电路送到外围设备中。

该模块结构图如图3 所示。它主要包括数据位宽变换模块和AES 加密单元。在USB 模 块数据接收和处理的位宽为8,而AES 加密模块中,明文和密钥的位宽为128,所以在USB 模块将接收来的数据包解包后所获得的数据不能直接加密,需要进行位宽调整后才可以加 密。数据位宽变换模块的功能就是将PL 解包后的8 位数据连接成128 位后再送入AES 加密 单元;AES 加密单元将送入的128 位明文与密钥存储器中的密钥进行十轮AddRoundkey、 SubBytes、ShiftRows、MixColumns 变换后完成明文加密,并将加密后的数据(密文)送入外 部存储器或通过WISHBONE 接口电路送到外围设备中。

2.2 性能分析

本文采用Stratix 系列的EP1S10F484C5 芯片对该系统进行验证。

2.2.1 USB2.0 模块的性能分析

下表为USB 模块综合后的性能参数:

USB 总线因其具有高速度、即插即用、功耗低等特点,深受广大用户的青睐。但USB 规范本身并未考虑数据传输时的安全性问题,所以它的安全性能低,不适合用来传输安全性 要求较高的信息。本文在研究USB2.0 规范以及应用密码学等安全防护技术的基础上,提出 一个基于ASIC 的整体解决方案。目的是用硬件描述语言设计一个既符合USB2.0 规范,同 时又可以将流经该接口芯片的数据进行自动加密的专用集成电路。最后,对所设计的系统在 FPGA 上进行验证,给出系统在FPGA 上所耗用的资源以及性能参数,对得到的数据进行分 析。

1 相关知识

1.1 USB 简介

从USB1.0 版本发布到2.0 版本,中间经历了多次版本更新。从1998 年7 月的Windows98 开始,USB 外围设备开始陆续出现,同时也成为最受欢迎的接口.它的优点为:容易使用、 传输速度快、低价位、低能耗、高稳定性、操作系统支持、外围设备的支持、有弹性.缺点 为:缺乏对数据安全性的考虑、缺乏对旧硬件的支持、点对点的通信、速度的限制、距离的 限制、硬件的错误或故障、协议的复杂性、版权费。

1.2 AES 简介

1.2.1 原理及起源

AES(Advanced Encryption Standard)是由美国国家标准与技术研究所于1997 年提出征集 该算法的公告并最终选定了两个比利时研究者Vincent Rijmen 和Joan Daemen 发明的 Rijndael)算法,并于2001 年正式发布了AES 标准。

1.2.2 AES 工作流程

Rijndael 算法本质上是一种对称分组密码体制,采用代替/转换网络,每轮由三层组成: 线性混合层确保多轮之上的高度扩散;非线性层由16 个S 盒并置起到混淆的作用;密钥加 密层将子密钥层异或到中间状态。Rijndael 是一个迭代分组密码,其分组长度和密钥长度都 是可变的,只是为了满足AES 的要求才限定处理的分组大小为128 位。而密钥长度为128 位、192 位或256 位,相应的迭代轮数Nr 为10 轮、12 轮、14 轮。可以抵御强大和实时的攻击。

2 系统解决方案

2.1 系统原理

本文主要目的是要设计一个既符合USB2.0 规范的数据接收和发送,又可以对接收到的 数据进行自动加密的专用集成电路的设计,并将所设计的系统用FPGA 对其进行功能验证。

该系统由两大模块组成:USB 模块和AES 加密模块。 系统结构如图1 所示:

|

2.1.1 USB 接口模块原理

该模块实现了符合USB2.0 规范的数据处理以及不同的外设与计算机的互连和数据通 信。 该模块的主要功能包括:

(1) 完全支持 USB2.0 规范,提供全速模式和高速模式,其数据率分别为12Mbit/s 和 480Mbit/s。

(2) 支持 WISHBONE 接口电路和该模块之间采用DMA 方式进行数据通信。

(3) 模块的挂起/恢复功能。 该模块结构如图2 所示。其中。PHY 模块负责将数据发送到与USB 连接器相连的计算 机,或接收来自计算机的数据;UTMI(数据通用收发宏单元接口)与PL(协议层)模块及内部 数据存储器、控制寄存器相连负责保持通信数据的格式符合USB2.0 规范中的协议格式; WISHBONE(主接口电路)是内部数据存储器、控制寄存器与外部设备之间的通信桥梁。

|

2.1.2 AES 模块原理

该模块负责将USB 模块接收并解包的数据进行加密然后将加密后的数据存入外部存储器或通过WISHBONE 接口电路送到外围设备中。

该模块结构图如图3 所示。它主要包括数据位宽变换模块和AES 加密单元。在USB 模 块数据接收和处理的位宽为8,而AES 加密模块中,明文和密钥的位宽为128,所以在USB 模块将接收来的数据包解包后所获得的数据不能直接加密,需要进行位宽调整后才可以加 密。数据位宽变换模块的功能就是将PL 解包后的8 位数据连接成128 位后再送入AES 加密 单元;AES 加密单元将送入的128 位明文与密钥存储器中的密钥进行十轮AddRoundkey、 SubBytes、ShiftRows、MixColumns 变换后完成明文加密,并将加密后的数据(密文)送入外 部存储器或通过WISHBONE 接口电路送到外围设备中。

|

2.2 性能分析

本文采用Stratix 系列的EP1S10F484C5 芯片对该系统进行验证。

2.2.1 USB2.0 模块的性能分析

下表为USB 模块综合后的性能参数:

- 实现WUSB设备控制器的设计考虑因素(09-12)

- 基于USB2.0的高速无线数传接收设备的数据接收存储方法(09-09)

- 四种短距离无线监控解决方案的性能对比(09-16)

- Wibree:一个可供选择的新无线联网技术(11-07)

- TI 单芯片手机多媒体电话解决方案(12-01)

- 蓝牙技术硬件实现模式分析(01-11)